# System-Level Power Optimization: Techniques and Tools

LUCA BENINI

Università di Bologna

and

GIOVANNI DE MICHELI

Stanford University

This tutorial surveys design methods for energy-efficient system-level design. We consider electronic systems consisting of a hardware platform and software layers. We consider the three major constituents of hardware that consume energy, namely computation, communication, and storage units, and we review methods for reducing their energy consumption. We also study models for analyzing the energy cost of software, and methods for energy-efficient software design and compilation.

This survey is organized around three main phases of a system design: conceptualization and modeling, design and implementation, and runtime management. For each phase, we review recent techniques for energy-efficient design of both hardware and software.

Categories and Subject Descriptors: B.7.2 [Integrated Circuits]: Design Aids; B.8.2 [Performance and Reliability]: Performance Analysis and Design Aids; C.1.0 [Processor Architectures]: General; D.2.2 [Software Engineering]: Design Tools and Techniques

General Terms: Design

### 1. INTRODUCTION

A system is a collection of components whose combined operations provide a useful service. Components can be heterogeneous in nature and their interaction may be regulated by some simple or complex means. Most systems are either electronic in nature (e.g., information processing systems) or contain an *embedded* electronic subsystem for monitoring and control (e.g., vehicle control). In this survey we consider electronic systems or subsystems; for the sake of simplicity, we refer to both as systems.

This work was supported in part by NSF under grant CCR-9901190, and in part by the MARCO Gigascale Research Center.

Authors' addresses: L. Benini, DEIS, Università di Bologna, Bologna, Italy; G. De Micheli, CSL, Gates Computer Science, Rm. 333, Stanford University, 353 Serra Mall, Stanford, CA 94305; email: nanni@stanford.edu.

Permission to make digital/hard copy of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage, the copyright notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee.

© 2000 ACM 1084-4309/00/0400-0001 \$5.00

ACM Transactions on Design Automation of Electronic Systems, Vol. 5, No. 2, April 2000, Pages 115-192.

System design consists of realizing a desired functionality while satisfying some design constraints. Broadly speaking, constraints delimit the design space and relate to the major design tradeoffs between system usefulness versus cost. System usefulness is tightly coupled with performance, i.e., the number of tasks that can be computed in a time window (system throughput) as well as the time delay to achieve a task (latency). Design cost relates to design and manufacturing costs (e.g., silicon area, testability) as well as to operational costs (e.g., power consumption, energy consumption per task, dependability).

In recent years the design tradeoff of performance versus power consumption has received much attention because (i) of the large number of mobile systems that need to provide services with the energy releasable by a battery of limited weight and size; (ii) the technical feasibility of high-performance computation due to heat extraction; (iii) concerns about the operating costs of large systems caused by electric power consumption as well as the dependability of systems operating at high temperatures because of power dissipation. (As an example, a data warehouse of an Internet service provider with 8000 servers needs  $2\,MW$ .)

Recent design methodologies and tools have addressed the problem of *energy-efficient design*, aiming to provide system realization while reducing its power dissipation. Note that energy/power optimization under performance constraints (and vice versa) is both hard to formulate and solve, when considering all degrees of freedom in system design. Thus we need to be satisfied with the notion of "power reduction" or with power minimization in a local setting. We use the term "energy-efficient design" to capture the notion of minimizing/reducing power and/or energy dissipation in system design, while providing adequate performance levels.

It is interesting to compare the evolution of goals in electronic system design with those of mechanical design, and in particular with combustion-engine design. In the beginning, achieving a working design was the engineer's goal, which was superseded by the object of achieving high-performance design. Later, energy efficiency in design was mandated by environmental and operating costs. In this respect, mechanical system design faced the problems of energy efficiency earlier, because of the larger consumption (as compared to electronic systems) of nonrenewable resources. Nevertheless, the energy consumption of electronic systems will scale up as they become more complex. Thus, economic, ecological, and ethical reasons mandate the development of energy-efficient electronic system designs.

## 2. SYSTEM ORGANIZATION AND SOURCES OF POWER CONSUMPTION

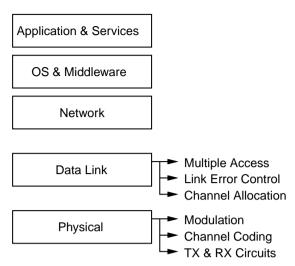

Typically, an electronic system consists of a hardware platform, executing system, and application software. Energy-efficient design requires reducing power dissipation in all parts of the design. When considering the hardware platform, we can distinguish three major constituents consuming significant energy: (i) *computation* units; (ii) *communication* units; and (iii)

storage units. Energy-efficient system-level design must address the reduction and balance of power consumption in all three constituents. Moreover, design decisions in a part of a system (e.g., the micro-architecture of a computing element) can affect the energy consumption in another part (e.g., memory and/or memory-processor busses).

Analyzing the hardware platform in more detail, we can distinguish integrated circuit (IC) components and components, such as *peripherals*, realized with other technologies. Peripherals may consume a significant fraction of system power. Examples of peripherals include electro-mechanical components (e.g., hard-disk drives) and electro-optical units (e.g., displays), which may consume a significant fraction of the overall power budget. Energy-efficient design of peripherals is beyond the scope of this survey; but, nevertheless, we will describe power management techniques that aim at shutting peripherals down during idle periods, thus drastically decreasing overall energy consumption.

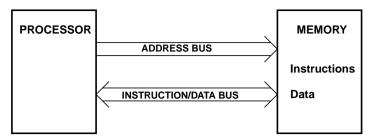

Since software does not have a physical realization, we need appropriate models for analyzing the impact of software on hardware power consumption. Choices for software implementation (i.e., system-level software, application-level software, and their compilation into machine code) also affect the energy consumption of the three aforementioned componenets For example, software compilation affects the instructions used by computing elements, each one bearing a specific energy cost. Software storage and data access in memory affect energy balance, and data representation (i.e., encoding) affects power dissipation of communication resources (e.g., busses).

Modeling electronic systems is very important in order to abstract their characteristics and design objectives. Most textbooks, e.g., Hennessy and Patterson [1996], define architecture in the context of systems having one major computation engine. Thus, the instruction set architecture (ISA), which is the programmer-visible instruction set, provides a neat abstraction between hardware and software. Most recent electronic systems can be characterized as having several processing engines, operating concurrently and communicating with each other. Examples can be provided by chips for multimedia application, with several processing units, including a generalpurpose processor core, a digital signal processor (DSP) core, and a microcontroller core. In general, we can think of systems as executing parallel threads of execution, some on processors (with different ISAs) and some directly in hardware. Thus the notion of system organization, or macroarchitecture, is the appropriate high-level abstraction for implementation models. Conversely, we refer to the architecture of a single processor core as a micro-architecture. For brevity, we use the term "architecture" when its meaning is clear from the context.

System design consists of mapping a high-level functional system model onto an architecture. Energy efficient system design must be supported by a design flow that takes power consumption into account in all its steps. Tackling power dissipation in later design stages is generally an ineffective strategy because most key decisions on system organization have already

Hardware, software and runtime management

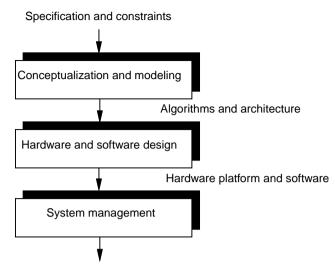

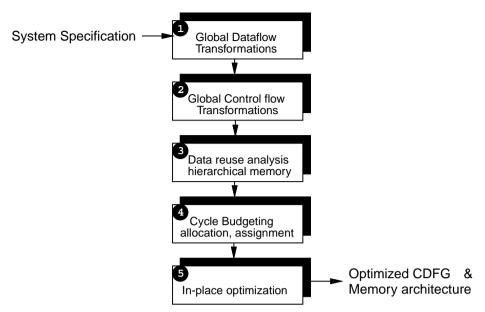

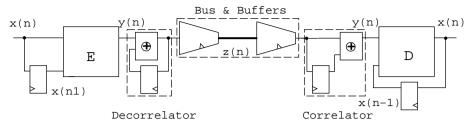

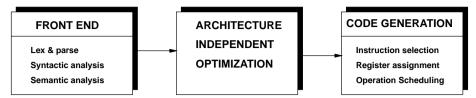

Fig. 1. Main steps in system design flow.

been taken. On the other hand, power-conscious design should not be limited to the early design stages alone because energy efficiency ultimately depends on detailed implementation issues. In this work we assume a top-down system design flow, summarized in Figure 1. We distinguish three major phases: (i) conceptualization and modeling; (ii) design; (iii) management.

In the first stage, starting from a system-level specification, the system architecture is outlined, together with the boundary between hardware and software. Clearly, at this stage, the designer has a very abstract view of the system. The most abstract representation of a system is the function it performs. The choice of the algorithm for performing a function (whether implemented in hardware or software) affects system performance and power consumption. In addition, the choice of the physical parameters (e.g., word-width) for the implementation of an algorithm is a degree of freedom that can be used in trading-off quality of service (e.g., image quality) for energy efficiency. Moreover, algorithms can have approximate implementations, i.e., certain operations may be implemented with limited accuracy to reduce energy costs. For example, a cos(x) function can be approximated as a Taylor expansion  $1 - x^2/2 + x^4/24$ . Furthermore, it may be approximated as  $1 - x^2/2 + x^4/32$ , which is simpler to realize than the Taylor expansion because the division of the last term by 32 can be done by shift. During system conceptualization and modeling, the system architect takes the key decision on algorithms (i.e., how to obtain the specified functionality), and hardware architectures (i.e., what is the hardware support required for implementing the functionality with the selected algorithm), but he/she does not deal with implementation details, which are left to the design phase.

During system design, organizational and technological choices are performed. At this stage, we are concerned with implementing the hardware architecture sketched in the conceptualization and modeling steps. When the architecture contains programmable components, we also need to produce the (embedded) software that executes on them. Design is supported by hardware synthesis tools and software compilers. Energy efficiency can obtained by leveraging the degrees of freedom of the underlying hardware technology. Several new technologies have been developed specifically for low-power systems [Vittoz 1994; Mendl 1995]. Notable examples are (i) technologies for very low supply-voltage operations; (ii) support for multiple supply voltages on a single chip; (iii) techniques for handling dynamically-variable supply voltage and/or clock speed. Special-purpose technologies are not the only way to design low-power systems. Even within the framework of a standard implementation technology, there are ample possibilities for reducing power consumption. It is important to note that tools for energy-efficient design may leverage degrees of freedom at various levels of abstraction. For example, a hardware resource scheduler may choose components operating at different voltages, and thus exploit both the freedom in choosing the time frames for executing the resources (as allowed by data flow) as well as resources operating with different supply voltages (as allowed by the technology) and with correspondingly different delay/power characteristics.

Once a system has been realized, and is deployed in the field, system-level software manages resources and thus controls the entire hardware platform, including peripherals. The main purpose of the last design phase is to equip the system with an energy-efficient runtime support system. Lightweight operating systems, i.e., those that avoid performing functions unimportant for the specific system application, are key to energy-efficient system design. Dynamic power management techniques allow systems to adapt to time-varying workloads and to significantly reduce energy consumption.

To help classify and compare energy-efficient system design techniques, we organize our survey by following a two-dimensional taxonomy. The first dimension corresponds to the design steps of Figure 1. The second differentiates the power consumed in computation, storage, and communication. Needless to say, a complete design methodology should cover all dimensions fully. Unfortunately, the state of the art has not yet converged to a complete methodology, and many techniques in the literature are applicable only during a single step in the design flow and focus on only one of the causes of power consumption.

The rest of this paper is organized as follows. We first review system modeling and conceptualization techniques for energy-efficient system design. Second, we address hardware synthesis and software compilation for low-power consumption. Finally, we consider system management issues. Within each design phase, we describe how various power optimization techniques target computation, storage, and communication energy consumption.

### 3. SYSTEM CONCEPTUALIZATION AND MODELING

In this section we focus on the early stages of the design process, when the boundary between hardware and software is not yet decided. Many authors refer to this design phase as *hardware/software codesign* [Wolf 1994; De Micheli and Gupta 1997]. We take a slightly different viewpoint. In our view, the key objective in this design phase is the creation of an abstract system model that will act as a frame for refinement and detailed design. We first survey system conceptualization and modeling styles, then outline the techniques proposed to steer the conceptualization process toward low-power solutions. Our main purpose is to identify a set of guiding principles for energy-efficient system design.

# 3.1 Models for System Specification and Implementation

System models are representations that highlight some characteristics while abstracting away some others. Typically, system models that capture all aspects of a design are complex and less useful than feature-specific models. Design of complex systems benefits from the orthogonalization of concerns, i.e., from decomposing the design problem into subproblems that are fairly independent of each other. The utilization of different, sometimes orthogonal, models is useful for capturing a design as well as those features most important to its designers.

$3.1.1\ Functional\ Models.$  Functional models are system specifications addressing functionality and requirements. A major distinction is between executable and nonexecutable functional models. Executable functional models capture the function that the system implements and allow designers to simulate system functionality. Some executable models are detailed enough to support synthesis of hardware components or software compilation; for example, models in hardware description languages (HDLs) such as Verilog HDL, or VHDL, and in programming languages such as C or C++.

Nonexecutable functional models highlight specific system features, while abstracting away some functional information. For example, the task graph model abstracts system functionality into a set of tasks represented as nodes in a graph, and represents functional dependencies among tasks with graph edges. The task graph is a nonexecutable functional model that emphasizes communication and concurrency between system tasks. Edge and node labelling are used to enrich the semantics of this model. For instance, node labels are used to represent communication bandwidth requirements, while node labels may store certain task computational requirements. Nonexecutable models are used when functionality is extremely complex or incompletely specified, which helps system architects to focus on just some facets of a complex system design.

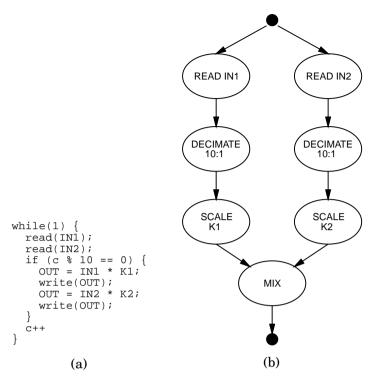

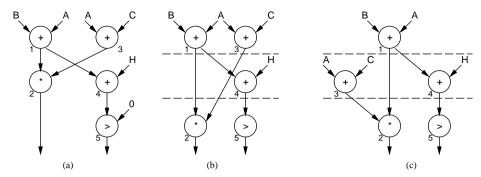

Example 3.1 Consider a simple system that performs decimation, scaling, and mixing of two data streams. The executable functional model for such a system, in the C language, is given in Figure 2(a). A task graph

Fig. 2. (a)An executable functional model (in C); (b) a nonexecutable functional model (a task graph).

nonexecutable model is shown in Figure 2(b). While the C specification fully expresses the functionality of the system, the task graph abstracts away functionality, but provides information on concurrency (nodes with no directed path between them can be executed concurrently) and on communication (the edges represent the flow of data between tasks).

Currently, there is no widespread agreement on specification forms for system design; hybrid styles are often adopted (e.g., task graphs with executable functional models for each task). These forms are useful in bringing many different aspects of the system together, and in helping designers to keep them consistent during refinement and optimization. The reader is referred to Gajski et al. [1994] and Lee and Sangiovanni-Vincentelli [1998] for recent surveys on system specification styles and languages. Energy-efficient system design requires both executable and nonexecutable functional models.

3.1.2 Implementation Models. Implementation models are used to describe the target realizations for systems. To cope with the increasingly larger complexity of electronic systems, such models need to have specific properties, including modularity, component-orientation, and hierarchy. Implementation models include structural models that describe systems as an assembly of components. Structural models are often used as intermedi-

ate representations within the design trajectory, from functional models to detailed implementation models (e.g., logic-level, mask-level models). On the other hand, structural models are sometimes used to capture design partitions among components that are an integral part of the specifications themselves.

Some implementation models blend structural information with functional and operational information. In Section 3.4 we present two implementation models that are relevant to energy-efficient system modeling and design: the *spreadsheet* model [Lidski and Rabaey 1996] and the *power state machine* model [Benini et al. 1998c]. The former expresses a combination of components and evaluates the overall energy budget. The latter captures the power consumption of systems and their constituents as they evolve through a sequence of operational states.

3.1.3 System Models and Design. Depending on the targeted application, functional and implementation models are exploited in different ways. We distinguish between special-purpose and general-purpose systems. Special-purpose systems are designed with a specific complex application in mind, e.g., MPEG2 compression, ABS brake system control. In this case the system design task can be stated in simple terms: finding a mapping from a system function onto a macro-architecture. In practice, most systems are realized using libraries of complex components such as processor cores. Thus, the first steps in system design consist of finding a suitable partition of the system specification into processors, memories, and applicationspecific hardware units. The choice of a processor for realizing a part of the system functionality means that the subsystem functionality will be compiled into software machine code for the corresponding processor. Conversely, the choice of application-specific hardware units implies that the functionality will be mapped into silicon primitives using synthesis tools. Overall, the allocation of system functions to processors, implying a hardware/software partition, is a complex task [De Micheli and Gupta 1997]. Whereas tools and methodologies for computer-aided hardware/software partitioning have been proposed, it is still often done by the designers themselves We comment on methods for computer-aided hardware/software partitioning for low power in Section 3.3.

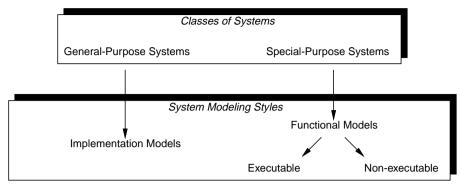

General-purpose systems are developed with no single application in mind, but with a flexible platform for a number of different applications; for example, personal digital assistants and portable computers. Functional models have little relevance for these systems, where the starting point is an architectural model and system design focuses on selecting the mix of components that best match design targets and constraints. Design of general-purpose systems emphasizes reuse of architectural templates and component families, in order to provide support to legacy applications and reduce time-to-market. The relationships among types of systems, models, and design flows are summarized in Figure 3.

Fig. 3. Taxonomy of system conceptualization and modeling styles.

In the next sections we survey energy-efficient design techniques, starting from executable, nonexecutable, functional, and implementation models.

# 3.2 Energy-Efficient Design from Executable Functional Models

System specifications can be done using mathematical formalisms, i.e., pure functional specifications that describe a mapping between inputs and outputs. For example, in a GPS receiver, the inputs are signals from the GPS satellites, the outputs are spatial coordinates, mapping is implicitly expressed by the solution of a set of linear equations where the coefficients of the unknowns are derived from the input data. Pure functional specifications are quite uncommon in practice, and functionality is usually specified through procedural executable models. The widespread use of procedural models stems from the fact that both HDLs and commonly used programming languages (e.g., C, C++, Java) have a procedural semantics.

Broadly speaking, the generation of procedural models is a way of providing a "solution recipe," i.e., an algorithm. Unfortunately, procedural models are usually fairly biased, since multiple algorithms can solve a mathematical problem. As an example, a *sorting* function can be done by different algorithms. Search for the "best" algorithm is typically a very hard problem due to the size of the search space. Nevertheless, different procedures require more/less computation, storage, and communication. Thus, according to the relative energy costs of these operations, and typically to the corresponding performance, one procedure may be better than another.

Algorithm selection. To limit the search space and allow some form of algorithmic exploration, some approaches take a hybrid functional-procedural approach based on algorithm selection [Potkonjak and Rabaey 1999]. Procedural specifications usually contain function calls, which can be seen as pure functional views of subtasks in a complex computation. Algorithm selection assumes the existence of a library with multiple algorithms for computation of some common functions. Furthermore, it is assumed that

the energy consumption and performance of the library elements on a given target architecture can be characterized beforehand. For each function call in the procedural specification, we can select the algorithm that minimizes power consumption while satisfying performance constraints.

Example 3.2 In their study of algorithm selection for low power, Potkonjak and Rabaey [1999] considered several different algorithms for discrete cosine transform (DCT) computation. As a target architecture, they considered fully application-specific hardware, synthesized with a high-level synthesis system. For each algorithm, a power-performance tradeoff curve was obtained by synthesizing a circuit with different supply voltages.

After library characterization, system optimization based on algorithm selection is performed. For each call to the DCT function in a complex procedural specification, a heuristic optimization procedure selects the DCT implementation and the supply voltage for the corresponding circuit that optimally trades-off performance for power.

Algorithm selection may also be made from an object-oriented viewpoint, in which algorithms are seen as methods associated with objects. Hence, selecting an object or, in traditional terms, an abstract data type, implies algorithmic selection as well as data structure selection. This approach is taken by Wuytack et al. [1997] and Da Silva et al. [1998], where it is demonstrated that abstract data type selection has a major impact on power dissipation. At a lower level of abstraction, Sacha and Irwin [1998] and Winzker [1998] show that number representation is also an important algorithmic design choice for low-energy DSP systems.

The algorithmic-selection approach has several shortcomings. First, it can be applied only to general-purpose primitives, whose functionality is well known, and for which many functionally-equivalent algorithms have been developed. Second, it neglects the impact of the interaction between the hardware implementing the function and that executing the remaining computations. Hence, precharacterizing the power consumption of the function in isolation may be inaccurate. These issues must be addressed by techniques for energy-efficient design, starting from a generic executable functional model, which is outlined next.

Algorithm computational energy. The semantic of a generic functional specification can be expressed by hierarchical control-data flow graphs (CDFGs), where nodes represent elementary operations, edges represent control and data dependencies among operations, and nested procedure calls correspond to transitions between successive hierarchy levels [Aho et al. 1988]. The CDFG contains complete information on the computation performed by an algorithm, seen as data manipulation and control flow. Hence, it is conceivable to be able to assess, through CDFG analysis, the energy cost spent by computation. This approach has been taken by some researchers [Chau and Powell 1992; Tiwari et al. 1996].

To estimate computational energy by CDFG analysis, we need first to characterize elementary operations with a computational energy metric,

then we need compositional rules to compute the total cost of a complex CDFG containing many elementary operations. Energy estimates of elementary operations can be obtained by assuming an implementation style and by extracting cost per operation through characterization experiments. Composition rules also depend on the implementation style, and account for the impact that the execution of an operation may have on the energy dissipated in the execution of other operations later in time. Cost per operation and composition rules have been developed for both processors [Tiwari et al. 1996] and custom units [Chau and Powell 1992].

Example 3.3 An early example of computational energy estimation is the power factor analysis (PFA), by Chau and Powell [1992]. The PFA technique targets pure data-flow computations. Elementary operations are the basic arithmetic operations. Operational energy is obtained by simulating arithmetic circuits with random white noise data and by computing average energy per evaluation. Total energy is computed by simply summing the energy of all operations. Using this simple model, it is possible to formulate several algorithms to minimize computational power. For instance, data-flow transformations based on algebraic manipulation, such as those proposed by Chandrakasan et al. [1995], can be driven by the PFA metric.

Algorithm communication and storage energy. Unfortunately, procedural specifications hide storage and communication costs, which are implicit in the representation. Therefore, a simple algorithm may require large storage, and thus efficiency of realization cannot simply be related to computational energy, especially when the energy cost of storage and data transfer is significant. Several researchers have observed that storage and communication requirements are related to the *locality* of a computation [Mehra et al. 1996; 1997; Catthoor et al. 1994]. Lack of locality in a highly sequential control flow implies that results computed very early are needed much later in time. Data variables have a long lifetime, thereby increasing storage requirements. Similarly, a highly parallel computation with significant communication between parallel threads is likely to require a complex and power-hungry communication infrastructure.

Estimating algorithmic locality from a CDFG is a difficult task because this information is not explicitly available. Nevertheless, a few locality analysis procedures have been developed for data-dominated algorithms, i.e., pure data-flow specifications. Mehra and Rabaey proposed an approach based on the analysis of the connectivity of a data-flow specification [Mehra et al. 1996]. Currently, however, locality analysis for general CDFGs is still an open issue.

Example 3.4 The technique developed by Mehra et al. [1996] to assess algorithm locality transforms a given DFG into a weighted graph, where edge weights are assigned through several heuristics that take into account the amount of data transferred on each edge of the original DFG. An optimal linear placement for the graph is then computed using Lagrangian

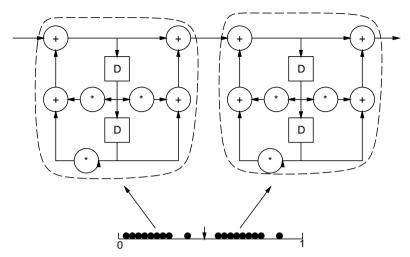

Fig. 4. Locality analysis for pure data-flow graphs.

minimization. Finally, the locality of the algorithms is assessed by detecting clusters in linear placement. Algorithms with poor locality have few and unbalanced clusters. As an example, consider the data flow of a fourth-order IIR filter, as shown at the top of Figure 4. The optimal linear placement of the corresponding weighted graph is shown at the bottom of the figure. Notice that linear placement has two natural clusters, which suggest that the algorithms has good locality.

In Mehra's approach, locality analysis is directly exploited to create loosely-connected clusters of operations that are mapped to different dedicated hardware units. This partitioning technique reduces the power consumed in the global interconnects of the hardware implementation of the initial DFG. In the example of Figure 4, the natural clusters of the data-flow graph, inferred from locality analysis, are shown by dashed lines.

It is important to observe that the relative energy cost of computation, communication, and storage is strongly dependent on the target architecture and technology. Consider for instance the relative energy costs of storage and computation. In traditional technologies, large DRAM memories cannot be integrated on the same die with logic circuits. Hence, the energy cost for storing data in large background memories involves off-chip communication, which is much more power-consuming than on-chip computation. This observation is the basic motivation behind the large body of work developed at IMEC [Catthoor et al. 1994], which focuses on algorithmic transformations for reducing memory requirements and rationalizing memory accesses. In contrast, recently developed technology, known as embedded DRAMs, enables the integration of large DRAMs with digital logic circuits on the same die. In this technology the balance may shift, and computation may have energy costs similar to memory access.

*Example 3.5* Consider two well-known video decompression algorithms, namely MPEG decoding and vector quantization. Roughly speaking, MPEG

decoding is based on computationally intensive inverse cosine transform (IDCT) and motion compensation procedures. But vector quantization decompression is based on lookups in a code decompression table; hence it is a memory-intensive approach. Meng et al. [1995] designed a low-power video decoder chip based on vector quantization. They claimed that vector quantization is very power efficient because decompression is simply based on a memory lookup, and does not require extensive computations, as in the case of MPEG decoding. This conclusion is true only if the decompression memory is on-chip. Indeed, this was the case in the design of Meng et al. If decompression had required off-chip memory access, MPEG decoding would probably have been more power-efficient.

Computational kernels. In pure, nonhierarchical data-flow computation, every elementary operation is executed the same number of times. This is a very restrictive semantic, even for data-intensive applications, since almost every nontrivial data processing algorithm involves some form of control flow and repetitive computation. Hence, most algorithms have loops, branches, and procedure calls that create a nonuniform distribution for the number of times each operation is executed. The well-known empirical "law" that states that most execution time is spent on a small fraction of a program is an equivalent formulation of the same concept. Such nonuniformity is very relevant for energy-efficient system design.

We call computational kernels [Wan et al. 1998; Henkel 1999] the inner loops of a computation, where the most time is spent during execution. Profiling an algorithm execution flow under "typical" input streams can easily detect computational kernels. To substantially reduce power consumption, each computational kernel is optimized as a stand-alone application and implemented on dedicated hardware that interfaces with the less frequently executed sections of the algorithm whenever the flow of control transitions into and out of the kernel. During system operation, when the computation is within a computational kernel, only the kernel processor is active (and dissipates power), while the rest of the system can be shut down. Otherwise, the kernel processor is disabled. In other words, kernel extraction forces mutual exclusiveness in hardware by limiting hardware sharing. For this reason, energy efficiency is usually obtained at the expense of silicon area and, in some cases, of marginal delay increases. These overheads should be taken into account when evaluating the potential of this approach.

The potential of computational kernels has been exploited by several optimization techniques at low levels of abstraction [Benini and De Micheli 1997]. Research on system-level computational kernels is still in its infancy. Two techniques with strong similarities have been proposed by Wan et al. [1998] and by Henkel [1999]. Both assume a system architectural template containing a general-purpose processor, and one or more application-specific processor which are synthesized when needed. Profiling data is collected on a system-level executable model. From profiling, the main computational kernels are extracted. The kernels are them synthesized in

hardware as application-specific processors. Increased energy efficiency is claimed based on the observation that performing a computation on dedicated hardware is usually one or two orders of magnitude more power efficient than using a general-purpose processor.

Example 3.6 MPEG audio decompression is well-suited for extraction of computational kernels. Profiling analysis has revealed that for almost any software implementation of the MPEG standard, most of the execution time is spent in two procedures: the modified inverse discrete cosine transform (MIDCT), and the sub-band synthesis filter. These procedures have little control flow, and mostly perform data manipulation (digital filtering). Hence, they are ideal candidates for a dedicated hardware implementation.

Notice that most current general-purpose and digital signal processors can easily perform MPEG decompression in real time; hence, from a performance viewpoint, mapping computational kernels in hardware is not needed. However, we can still exploit the energy efficiency of custom-hardware implementations of MIDCT and subband synthesis to reduce power dissipation.

Approximate processing. In many cases system functionality is not specified in a succinct fashion—fuzzy and flexible specifications are very common in the area of human sensory interfaces. Consider for instance a video interface such as wireless video phone. Even though we can provide a succinct specification on video quality (such as image resolution), it may impose excessively tight constraints on the design. Human users may be satisfied with low video quality, for instance when watching a television show, but they may require very high quality when reading a page on screen.

A few techniques take an aggressive approach to power reduction for applications where a well-controlled amount of noise can be tolerated. The key idea here is that power dissipation can be drastically reduced by allowing some inaccuracies in the computation [Vittoz 1994; Ludwig et al. 1996; Nawab et al. 1997; Hedge and Shanbhag 1998; Flinn and Satyanarayanan 1999]. Approximate computation algorithms can adapt this quality to power constrains and user requirements.

Example 3.7 An example application of approximate computation is digital filtering. By dynamically controlling the bit width of the processed data, it is possible to trade-off quantization noise for energy. In the finite-impulse response (FIR) filter architecture proposed by Ludwig et al. [1996], it is possible to dynamically change the bit width. The logic in the fanin and fanout of unused bit lines is disabled and does not consume power. Clearly, reduced bit-width computation is inaccurate, and the quality of the output is affected by quantization noise. In some applications, and for some operating conditions, this is tolerable.

## 3.3 Energy-Efficient Design from NonExecutable Functional Models

Many systems are not designed starting from executable functional models. In the early steps of system design, executable models may not be available, either because the specification is provided in natural language or because the definition of system characteristics is flexible and evolves as the design progresses. Furthermore, a complete description of system functionality is often extremely complex, and some high-level design issues must be addressed much before a complete executable functional model is available. As a result, many systems are designed without an executable specification.

Even when an executable specification does exist, designers may want to deal with a simplified, abstract view of the system, where only some specific characteristics are considered in detail, while many others are abstracted away. Thanks to the complexity reduction provided by abstraction, it is possible to rapidly explore the design space, at the price of an increase in the uncertainty of results.

A very common abstract system model, which still contains some information on functionality, but eliminates a lot of the detail needed in an executable specification, is the *task graph*, described in Section 3.1.1. Task graphs have been used in a variety of design environments much before energy efficiency became a primary concern. Hence, the main challenge in using this model for low-power design is in enhancing its semantics to include information on power dissipation.

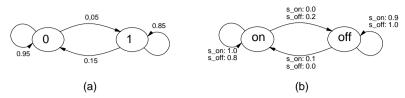

Several authors proposed techniques that start from a task graph specification for minimizing the power consumption at the system level [Brown et al. 1997; Kirovski and Potkonjak 1997; Dave et al. 1999; Hong et al. 1998a; 1998b; 1998c; Ishihara and Yasuura 1998a; Qu and Potkonjak 1998]. These techniques attempt to provide a solution for variations of the following design problem: Given a task graph specification and an architectural template for system implementation with several functional units, find the mapping of tasks to functional units that minimizes energy while respecting performance constraints. Notice that we use the term "mapping" to denote both the binding of a task to a given computational resource and the scheduling of multiple tasks to the same resource.

The target architectural templates have considerable flexibility: processing elements, interconnect, and memory architecture are application-specific; more particularly, processing elements can be core processors, custom hardware, or programmable logics (FPGAs). Memory size and type (SRAM, DRAM, Cache, etc.) can be selected. Communication is supported through system busses. In some cases, supply voltage is an additional degree of freedom. In principle all sources of power dissipation can be addressed at this level, although the key issue is how to reliably estimate the power consumed by a given mapping. Needless to say, at this level of abstraction, only rough estimates can be performed to help designers compare design alternatives, but these estimates should never be used for design validation

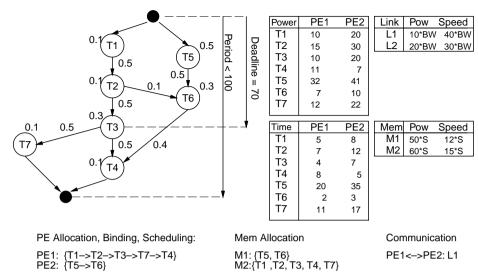

Fig. 5. Power estimation for nonexecutable functional models: Task graph.

(where only small errors with respect to the final implementation are acceptable).

In the approach proposed by Kirovski and Potkonjak [1997] and Dave et al. [1999], it is assumed that the power consumed by each task when mapped to each compatible class of processing elements is known or is obtained by precharacterization. It is also assumed that memory usage and communication requirements for each task are known beforehand. Given a mapping of a task graph into hardware, the total power consumed by functional units is computed summing the power consumed by each task when executing on the functional unit specified by the mapping. Task power consumption for storage is computed by multiplying the expected number of accesses of each task by the power-per-access of the memory that stores the task's data set. Communication power is computed by multiplying the number of data transfers initiated by the task by the cost-per-data transfer of the system bus used for communication.

Example 3.8 Consider the task graph shown in Figure 5. Two performance constraints are specified. The execution period of the entire task graph must be less than 100 time units; furthermore, execution of task T3 must terminate by time 70. Tasks (i.e., nodes) are labeled with memory usage. Edges are marked with communication bandwidths. We have two types of processing elements, PE1 and PE2 (e.g., two different core processors), two types of memories, M1 and M2 (e.g., SRAM and DRAM), and two types of communication channels, L1 and L2 (two different busses). The execution time and power (energy) consumption of each task on each processor is shown in the tables labeled "Time" and "Power." The energy and time costs of communication are a function of bandwidth, and are collected in the table labeled "Link." The energy and time costs for memory are a function of memory size, and are shown in the table marked "Mem."

An allocation of processing elements, with binding and scheduling, is shown at the bottom of Figure 5. Memory and communication channel allocation is shown as well. With this information, we can compute performance and power for the task graph. Let us consider computation energy first:

$$E_{PE} = E_{PE1} + E_{PE2} = (10 + 15 + 10 + 11 + 12) + (41 + 10) = 109$$

Observe that computation energy for a shared processor is computed by simply summing the energies required by all tasks running on it. Storage energy is computed by first calculating total memory size for each memory type and then multiplying it by its energy-per-size value (from table "Mem"):

$$E_{Mem} = E_{M1} + E_{M2} = (0.1 + 0.1 + 0.3 + 0.1 + 0.1) \cdot 60 + (0.5 + 0.3) \cdot 50 = 88$$

Finally, communication energy is obtained by first computing the total communication bandwidth between the two PEs and then multiplying it for the energy-per-bandwidth of the selected communication link:

$$E_{Com} = E_{PE1 \to PE2} + E_{PE2 \to PE1} = (0.1 + 0.4) \cdot 20 = 10$$

The total energy is  $E=E_{PE}+E_{Mem}+E_{Com}=109+88+10=206$ . Speed is computed in a similar fashion.

The main issues in power estimation (and, as a consequence, optimization) for nonexecutable models are the need for exhaustive precharacterization and loss of accuracy caused by lack of information on the effects caused by hardware sharing. Precharacterization requires estimating the power consumed by each task on every possible hardware implementation, and for every possible voltage supply (if multiple supply voltages are available). This process can be extremely onerous for large task graphs and for large libraries of processors. Furthermore, estimating the power consumed by a task's implementation on dedicated hardware is far from trivial, since such an implementation may be unavailable in the early phases of system design.

Whenever a hardware resource is shared among several processes, it is generally very hard to provide an accurate estimate of the power cost of sharing without having functional information. Consider for instance a shared processor core with an on-chip cache. If two processes share a processor, the total power consumption is likely to be substantially larger than the sum of the power consumed by the two processes running as a single task. The overhead is caused by task-scheduling support (e.g., context switching, preemption, synchronization on mutually exclusive resources) and by cache locality disruption caused by the different work sets of the two processes. Overhead estimates depend strongly on functional information, which is not available when dealing with abstract task graphs.

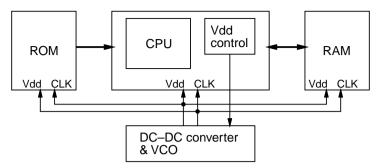

|           | #Comp | Vdd | I <sub>IDLE</sub> | I <sub>ON</sub> | %idle | %on   | I (mA) |

|-----------|-------|-----|-------------------|-----------------|-------|-------|--------|

| Processor | 1     | 3.3 | 0.5               | 50              | 0.3   | 0.7   | 35.15  |

| DRAM      | 1     | 3.3 | 0.1               | 12              | 0.3   | 0.7   | 8.43   |

| FLASH     | 5     | 3.3 | 0.0               | 9               | 0.3   | 0.7   | 31.5   |

| IR        | 1     | 3.3 | 0.0               | 64              | 0.95  | 0.05  | 3.2    |

| RTC       | 1     | 3.3 | 0.0               | 0.1             | 0     | 1     | 0.1    |

| DC-DC     | 1     | 3.3 | 0.1               | 5.5             | 0.01  | 0.99  | 5.44   |

|           |       |     |                   |                 |       | Total | 83.82  |

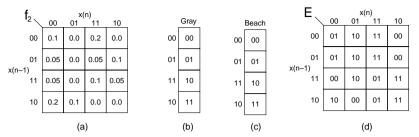

Fig. 6. Spreadsheet power model for an electronic agenda.

## 3.4 Energy-Efficient Design from Implementation Models

Many system designs are upgrades from older products and bear strong backward compatibility constraints. Such design often exploit commodity components connected through standard interfaces (e.g., PCI or USB busses). Thus, system modeling may be constrained from the beginning to using specific parts and interconnection topologies. Implementation models are useful in reasoning about different implementation options and the corresponding energy impact.

The spreadsheet model. In this design flow, executable functional models are never available, and rapid prototyping on breadboards is a common technique to obtain running hardware for measurement and test purposes. Unfortunately, prototyping is a time-consuming process, and designers need to have first-cut estimates of power consumption early in the design flow. To support this requirement, a few component-based power estimation approaches have been developed. The tool of choice for back-of-the-envelope power estimation is a standard spreadsheet. To estimate the impact of a component on the power budget, its dissipation is extracted from the data sheets and entered in the spreadsheet. Total power is obtained by simply summing over all components. This technique, which is very straightforward, is widely used and is often the only option available to designers.

Powerplay, developed by Lidsky and coauthors [Lidski and Rabaey 1996] is a web-based spreadsheet that offers the opportunity for component exploration in a distributed environment. This tool offers a library of power models at several levels of accuracy, starting from a constant power value up to complex activity-sensitive models that require a fair amount of input information from the designer.

Example 3.9 Consider a simple general-purpose system, such as an electronic agenda. The system is built around a microcontroller with 1MB of RAM memory. 2MB of flash memory is used to store firmware. Additional 8MB of flash memory is used to store user data. A PC interface is available through an IR link (implemented by a single integrated component).

The main user interface is through an LC display, with a touch-sensitive surface that can be written with a stylus. The system also contains a real-time clock chip with a quartz oscillator, and a stabilized DC-DC converter to power the components. All components are powered at 3.3 volts.

The power consumption of all components is taken from data sheets and collected in a spreadsheet, shown in Figure 6. For each component, the worksheet reports (i) component count, (ii) voltage supply value, (iii) current absorbed when idle, (iv) current absorbed when active, (v) percentage idle time, (vi) percentage active time, and (vii) average current absorbed. The average current (in mA) is computed as  $I = N_{components} \cdot (I_{idle} \cdot frac_{idle} + I_{on} \cdot frac_{on})$ . The total current absorbed is reported in the lower right-hand corner. To compute average power consumption, we multiply I by  $V_{dd}$ . We obtain  $P_{avg} = 276.6 \,\mathrm{mW}$ .

The main limitation of spreadsheets is that they do not model interactions among components. Also, spreadsheets require substantial user intervention to take into account component utilization. Consider for instance the power consumed by memory, which is strongly dependent on access frequency. In a spreadsheet model, the designer must estimate expected memory utilization and use it to scale memory power. In other words, whenever power dissipation depends on the interaction of a component with the rest of the system, the spreadsheet model falls short.

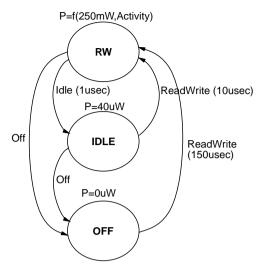

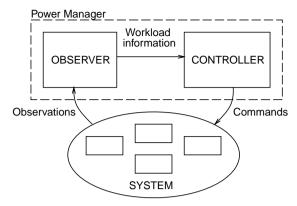

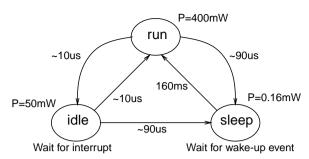

**Power state machines**. To mitigate the shortcomings of spreadsheets, Benini et al. [1998c] developed an abstract state-based model for system components, called a *power state machine* (PSM). In a power state machine, states represent modes of operation, while arcs represent legal transitions between modes of operation. States are labeled with power dissipation values, transitions are labeled with *triggering events*, *energy costs*, and *transition times*. A triggering event is an external stimulus that forces a state transition.

A system description of this model is a structural network of system components. A power state machine and, optionally, a functional model are specified for each system component. The functional model is an abstract specification of component behavior, which specifies how to respond to external events, possibly generating new events. A system description can be simulated. An external event source, representing the environment, drives the model. Clearly, this abstract simulation bears little resemblance to a functional simulation, but it offers the opportunity of tracking the power states of system components.

When all state machines are single state and no events are generated, the PSM model becomes equivalent to the spreadsheet model. However, PSMs offer the possibility of (i) studying how the system reacts to different workloads; (ii) modeling interactions between components; and (iii) analyzing the effects of power management. The main limitation is that it requires more complex component models than a spreadsheet, and some

Fig. 7. Power-finite state machines for a memory component.

effort on the designer's part in describing the abstract specification of component behavior.

Example 3.10 The power state machine for a memory component is shown in Figure 7. There are three power states, namely "read/write" (RW), "idle," and "off." Each state is characterized by a power consumption level. Notice that in the active state, power is a function of memory activity (i.e., read/write traffic into memory). Edges are marked with external events that, when asserted, force the transitions. Edges are also labeled with transition times When the transition time is not reported, it is assumed to be instantaneous.

#### 4. SYSTEM DESIGN

System modeling and conceptualization yield a hardware/software partition as well as a macro-architectural template and a set of procedures. System design consists of refining the hardware model of this template into computation, memory, and communication units. Different design flows, often based on computer-aided synthesis, support the mapping of these units into low-level detailed models ready for manufacture [De Micheli 1994]. When the template, as is most often the case, provides for programmable (core) processors to execute procedures, then software must be developed (or synthesized) and then compiled for the target cores.

The balance between software and hardware can vary widely, depending on the application and on the macro-architecture. Even though dedicated hardware is more energy efficient than software running on core processors, the latter has many compensating advantages, such as flexibility, ease of late debugging, low-cost, and fast design time. For these reasons,

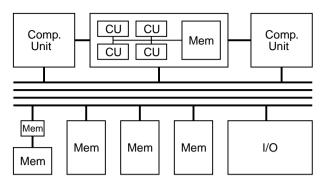

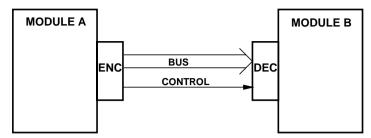

Fig. 8. Generic template for system hardware architecture.

core-based solutions are also present in energy-efficient system design. Nevertheless, most systems require some amount of hardware design.

This part of the tutorial is dedicated to the analysis of system design issues. We assume that conceptual analysis and modeling has been carried out. Therefore, the boundary between hardware and software and the macro-architectural template is set. In the next section, we focus on design of system hardware, with special emphasis on synthesis-based approaches. We consider only high-level system design techniques, and refer the reader to Macii et al. [1998]; Raghunathan et al. [1998]; Chandrakasan and Brodersen [1995]; and Rabaey and Pedram [1996] for a comparative analysis of methods for energy-efficient chip design (i.e., micro-architectural synthesis, logic synthesis, and physical design of ICs). We then report in Section 4.2 on software design and compilation. Needless to say, almost every conceivable system design flow entails both hardware and software synthesis, and it is often difficult to separate them.

## 4.1 Hardware Synthesis

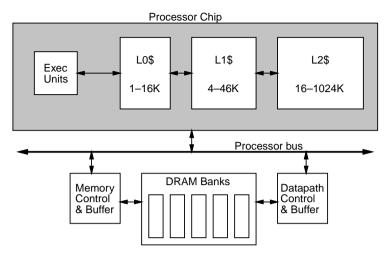

The outcome of system modeling and conceptualization is a hardware template, which is the starting point for hardware design. Most systems can be described as instances of a basic template, shown in Figure 8. The figure depicts a heterogeneous hardware architecture containing several computation units, memory, and interconnects. Generality can be increased by allowing computation units to be hierarchical. Data processing and control are carried out by computation units, whose micro-architecture can range from fully application-specific to general-purpose. At one extreme, we have a dedicated hardware processor that performs a single function, with limited or no flexibility. At the other extreme, we just instantiate a core processor that can be programmed to perform any function. Several degrees of customization exist in between, depending on the granularity of the blocks employed for building the micro-architecture. We survey techniques for energy-efficient design and synthesis of computation units in Section 4.1.1.

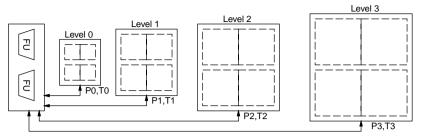

Storage resources are usually organized as a *memory hierarchy*. Memories at low hierarchy levels are small, fast, energy efficient, and dedicated

to a single processor, or shared among a small number of them. Memory at high levels of hierarchy are large, relatively slow, and power hungry. The motivation for hierarchical memory organization is exploitation of temporal and spatial storage locality. Depending on the specific design flow, the degrees of freedom in memory hierarchy design can vary widely. At one extreme, we have a fixed hierarchy, where the only design parameter that can be controlled is memory size for some levels of the hierarchy. At the other extreme, we have a fully-flexible memory hierarchy. Low-power memory design techniques are surveyed in Section 4.1.2.

Communication channels are also hierarchical. Local communication has short range, and involves a reduced number of terminals (the most common case is two). Thus, it is fast and power efficient. Long-range global communication requires complex protocols, it is relatively slow and power inefficient. Nevertheless, it is required for supporting nonlocal information transfer. For simple macro-architectures, a single-level communication hierarchy is often employed. In complex architectures, communication resources can be organized in a hierarchical fashion. Energy-efficient communication channel design is analyzed in Section 4.1.3.

Even though we analyze computation, storage, and communication separately, it should be clear that it is impossible to design well-balanced systems by focusing on one of these areas only, and completely disregarding the others. Ideally, we would like to tackle all design issues at the same time, and achieve a globally optimum design. In most practical cases, however design quality benefits from focusing on just a few facets of the power optimization problem at one time, while keeping the remaining issues in the background. A well-balanced design is obtained by adopting a design flow where design challenges are prioritized and solved in sequence, possibly with iterations.

4.1.1 Synthesis of Computation Units. As mentioned above, data-processing units in an electronic system can be customized at different granularity levels. At the coarser granularity, we have processor cores. Cores are very successful in embedded system design because they reduce design turn-around time by moving all system customization tasks into the software domain. RISC processors are becoming very successful cores [Segars et al. 1995; Hasegawa et al. [1995], together with specialized processors for digital signal processing [Lee et al. 1997b; Mutoh et al. 1996; Verbauwhede and Touriguian 1998].

Cores are easy to use and very flexible, and sometimes they are necessary. However, they are not power efficient when compared with custom hardware solutions. Consider, for instance, a very simple computation such as FIR filtering. A core processor can easily implement a FIR filter (by performing a sequence of multiplications and additions). On the other hand, a custom hardware architecture for FIR filtering can be created with just an adder, a multiplier, and a few registers. The energies (or, equivalently, energy-delay products) of these two architectures can easily be more than two orders of magnitude apart (obviously, in favor of the custom

architecture). This is just an example of a fairly general principle, which can be summarized as an "energy-efficiency versus flexibility" tradeoff [Nishitani 1999]. Any micro-architecture of a computation unit can be seen as a point on a tradeoff curve of energy-efficiency versus flexibility, intended to be reconfigured for implementing new computational tasks. We explore this curve, starting from application-specific units and moving toward more flexible, and less power-efficient architectures.

Application-specific units. This solution is biased towards maximum power efficiency, at the price of reduced flexibility. Typically, design starts from an initial specification that is executable and given in a high-level language, with constraints on performance, power, and area. The outcome is a circuit that can perform only the specified function. The most straightforward design flow for these units is based on hand-crafted translation of the executable specification into a register-transfer level (RTL) description, followed by hand-design of the data path and RTL synthesis of the control path. To reduce energy consumption, designers can leverage a large number of low-power RTL, logic-level and physical design techniques, which have been surveyed in several papers: [Pedram and Vaishnav 1997; Pedram 1996] and monographs [Chandrakasan and Brodersen 1995; Rabaey and Pedram 1996; Benini and De Micheli 1997].

An alternative design flow relies on automatic synthesis of the custom computation unit starting from the executable specification. This approach is often called behavioral synthesis (or, more generically, high-level synthesis). In essence, the main difference between RTL synthesis and behavioral synthesis is that in the latter the order in the time for executing elementary operations (scheduling) is not taken from the specification. In other words, as long as the external performance constraints (latency, throughput, and synchronization) on the specification are met, the hardware synthesizer is free to alter the computation flow and to schedule elementary operations in time. Behavioral synthesis has been studied for more than fifteen years, and its basic theory is described in several textbooks [De Micheli 1994; Gajski et al. 1992].

Behavioral synthesis of energy-efficient circuits has been intensively studied as well. The interested reader is referred to the survey by Macii et al. [1998] and the monograph by Raghunathan et al. [1998] for an in-depth analysis of algorithms and tools, as well as an extensive bibliography. In this section we focus only on the distinctive characteristics of behavioral synthesis for low power. The optimization target is dynamic power consumption, which is the product of four factors, namely: (i) clock frequency  $f_{CLK}$ ; (ii) the square of the supply voltage  $V_{dd}^2$ ; (iii) the load capacitance  $C_L$ ; and (iv) the average switching activity.

Probably the most direct way to reduce power is to scale down  $V_{dd}$ . Unfortunately, CMOS circuits get slower as  $V_{dd}$  decreases because CMOS transistors have smaller overdrive when they are on. Under these conditions, a good approach to reduce power consumption is to make a circuit faster than its performance constraint, then decrease the power supply

Fig. 9. Example of power-driven voltage scaling.

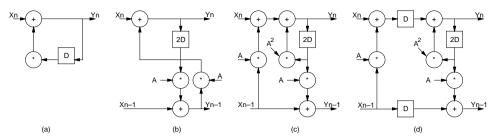

(obtaining a quadratic decrease in power) until the constraint is matched again. This *power-driven voltage scaling* approach was studied in depth by Chandrakasan et al. [1995] and Chandrakasan and Brodersen [1995]. One of its most interesting features is that it leverages well-established techniques for high-performance computation, such as parallelization, retiming, and pipelining to design energy-efficient circuits.

Example 4.1 An example of power optimization based on performance enhancement followed by voltage scaling is shown in Figure 9. The unoptimized specification is the data flow in Figure 9(a). Let us assume for simplicity that addition and multiplication by a constant take one time unit each. Thus, the critical path of the computation has length 2. First, loop unrolling is applied. The data-flow graph, unrolled once, is shown in Figure 9(b). The main purpose of this step is to enable speedup transformations. In Figure 9(c), constant propagation has been applied. Notice that both the number of operations performed every cycle and the critical path have increased with respect to (a). However, if we apply pipelining to the transformed data-flow graph, we reduce the critical path back to 2, but now we are processing two samples in parallel. The throughput has doubled. Hence, we can now scale down the voltage supply until delay has doubled, and we obtain a low-power implementation with the same throughput as the original specification. Voltage has been reduced from 5V to 2.9V, and power is reduced by a factor of 2.

The main limitation of power-driven voltage scaling is that it becomes less effective as technology scales down. In fact, fundamental reliability concerns are driving voltage supplies in modern submicron technologies to lower levels with each generation, reducing the headroom available for voltage scaling. Another issue is that most speedup techniques rapidly reach a region of diminishing returns when they are applied very aggressively. In other words, it may be easy to obtain good power saving by speeding up and scaling down voltage supply for circuits that are not optimized for performance, but further speeding up circuits that have already been optimized for performance is a challenging task, and may impose such complexity overhead as to be useless for power reduction.

Let us consider, for instance, two common speedup techniques: pipelining and parallelization. The point of diminishing returns for pipelining is reached due to pipeline register overhead. High-performance circuits are often deeply pipelined, and the levels of logic between stages are in the 15 to 20 range. In these deep pipelines, a significant fraction of the cycle time budget is taken by register setup and hold times and by clock skew. Even if we disregard timing issues, we cannot arbitrarily increase pipeline depth because registers would occupy excessive area and load the clock too much.

Parallelization (i.e., the speedup technique that duplicates part of the data path to allow more than one computation at the same time) hits the region of diminishing returns even earlier than pipelining, due to duplication of data path structures, imposes a large area overhead and increases wiring by a substantial amount.

Furthermore, pipelining and parallelization are limited by the presence of control-flow constraints such as loops and conditionals. To speedup computation past control-flow bottlenecks, we need speculation (i.e., carry out a computation assuming that conditionals will follow the most probable path) or predication (i.e., perform the computation under both the exits of a conditional). These techniques are power inefficient because they increase the amount of redundant computation.

The basic power-driven voltage scaling can be extended by allowing multiple supply voltages on a single die. Various behavioral synthesis techniques have been proposed to deal with multiple supply voltages [Chang and Pedram 1997; Raje and Sarrafzadeh 1995; Johnson and Roy 1996]. The key idea in these approaches is to save power in noncritical functional units by powering them with a down-scaled supply voltage. In this way delays are equalized, throughput is unchanged, but overall power is reduced. Real-life implementation of multisupply circuits poses nontrivial technological challenges (multiple power distribution grids, level-conversion circuits, DC-DC conversion on chip). Nevertheless, the technological viability of multisupply circuits has been proven on silicon [Usami et al. 1998b]. Hence, computer-aided design tools supporting this design style may gain acceptance in the design community.

Alternative approaches to power reduction have tackled all other dependencies of dynamic power, namely, clock frequency, load capacitance, and reducing switching activity. Frequency reduction has sometimes been dismissed in the literature as ineffective because it reduces power, but not energy [Chandrakasan and Brodersen 1995] (a system clocked at a low frequency performs less "computational work" in a time unit). This conclusion is drawn under two implicit assumptions: (i) the entire system is clocked by a single clock; and (ii) the goal is to minimize average energy. If we invalidate one of these assumptions, frequency reduction can be an effective technique.

Let us consider the first assumption. If we allow multiple clock domains on a single system, we can clock noncritical subsystems at slower frequencies, thereby saving significant power without compromising overall system performance. Systems with multiple clock domains (also known as *globally asynchronous locally synchronous* or GALS), clocked at different rates, are becoming viable [Brunvand et al. 1999], pushed by the ever-increasing cost of global clock distribution grids and by the fundamental limitation of

global synchronicity posed by the finite propagation speed of electric signals [Dally and Poulton 1998]. The potential of multifrequency clocks for energy-efficient computation is still largely unexplored, with a few notable exceptions. In the work of Chung et al. [1995], a clock-distribution technique is proposed where a low-frequency clock is propagated on long wires and multiplied locally. In the work by Hemani et al. [1999], a few single-clock industrial designs are transformed in GALS, reporting power savings up to 70%.

Clock frequency can be varied over time as well. One example of dynamic clock speed setting is *clock-gating*. If a system component is idle (i.e., it is not performing any useful work), we can set its clock frequency to zero, and nullify dynamic power consumption. Clock-gating is widely applied in real-life circuits [Gonzalez and Horowitz 1996; Tiwari et al. 1998; Benini and De Micheli 1997], and it is often presented as a technique for reducing switching activity [Benini and De Micheli 1997]. In fact, clock frequency reduction has the beneficial side effect of reducing switching activity. Clearly, clock-gating is an extreme case, but we can envision applications where clock speed is dynamically reduced or increased depending on system workload. Dynamic power management techniques, including dynamic clock speed setting, are surveyed in Section 5.1.2.

Regarding the second assumption, several authors have observed that in portable systems the ultimate target is not average energy reduction, but battery lifetime extension. If we model batteries as large ideal capacitors, then energy reduction translates directly into longer lifetime. Unfortunately, the ideal capacitor model is inaccurate for real-life batteries. More specifically, several authors [Martin and Sewiorek 1996; Wolfe 1996; Pedram and Wu 1999] have shown that the amount of charge that can be drawn from a battery depends not only on its capacity (which is a function of battery mass and chemistry), but also on the rate of discharge. In first approximation, effective capacity decreases with an increasing discharge rate, hence extracting charge from a battery at a slow rate can maximize the amount of computational work performed during a battery's lifetime.

Example 4.2 Martin and Sewiorek [1996] analyzed the effect of battery discharge rate on capacity, moving from the empirical formula  $C = K/I\psi$ , where K is a constant determined by battery physical design and chemistry; I is the average discharge current and  $\psi$  is a fitting coefficient. If  $\psi$  is zero, then the battery is ideal (constant capacity). For real-life batteries,  $\psi$  ranges between 0.1 and 0.7, depending on battery type. Martin showed that, when considering this relationship, reducing clock frequency (and, consequencetly, I) can increase the total computational work that can be performed over a battery's lifetime.

Power can be reduced by reducing average load capacitance. This problem has been studied in depth, and it is usually tackled at the level of physical-design abstraction [Pedram and Vaishnav 1997; Pedram 1996], which is outside the scope of this survey. At the system level, we can

Fig. 10. An example of scheduling and binding for reduced switching activity.

observe that there is a tight relationship between locality and average load capacitance. To understand this statement, observe that an architecture with good locality minimizes global communication, which is usually carried over long global wires with high capacitance load. This observation is the basis of the work by Mehra et al. [1996; 1997] on high-level partitioning for wire-load reduction.

Finally, we consider techniques for reducing average switching activity. At first this seems the most straightforward way to achieve this goal is to maximally reduce the number of basic operations. Srivastava and Potkonjak [1996] proposed a technique for transforming the data-flow graph of linear computation in such a way that the number of operations is minimized. This technique was later extended by Hong et al. [1997] to general data flows. It is important to see that minimizing the number of operations does not guarantee minimum power, since in general the power dissipated in executing an elementary operation depends on the switching activity of the operands.

Commonly-used arithmetic units dissipate more power when their inputs have high switching activity. We can reduce switching by increasing the correlation between successive patterns at the input of a functional unit. A few CDFG transformation techniques for facilitating the identification of sequences of operations with low switching activity have been presented in the past [Chandrakasan et al. 1995; Kim and Choi 1997; Guerra et al. 1998]. After CDFG transformations, behavioral synthesis transforms the CDFG into an RTL netlist. All behavioral synthesis steps (allocation, scheduling, and binding) have been modified to take into account switching activity (see Macii et al. [1998] for a survey), and behavioral synthesis of circuits with low switching activity is an area of active research. A prerequisite for the applicability of these approaches is some form of knowledge on input statistics for the hardware unit that is being synthesized.

Example 4.3 Consider the simple data-flow graph shown in Figure 10(a). The constraint on execution time is 3 clock cycles, the resource constrains are 2 adders, 1 multiplier, and one comparator. Figure 10(b) and (c) show two schedules compatible with resource constraints. Observe that

additions 1 and 3 share one of the operands. If we perform both additions with the same adder, its average switching per operation will be low, because one of the operands remains the same, and will dissipate less power than when performing two additions with uncorrelated inputs. In the schedule in Figure 10(b), however, it is not possible to implement additions 1 and 3 with the same adder, because the two operations are scheduled in the same control step. On the other hand, the schedule in Figure 10(c) does allow sharing, and it leads to a more energy-efficient implementation.

This simple example shows that in order to minimize power, allocation, scheduling, and binding algorithms must work synergistically. It is mainly for this reason that most behavioral synthesis approaches in the literature are based on iterative improvement heuristics [Chandrakasan et al. 1995; Kumar et al. 1995; San Martin and Knight 1996; Raghunathan and Jha 1997]. The main challenge in implementing effective optimization tools based on iterative improvement is estimating the power cost metric. Estimating power at the behavioral level is still an open problem for many aspects of implementation. Probably one of the most pressing issues is the mismatch between zero-delay switching activity and actual switching activity that may lead to macroscopic underestimates of power consumption [Raghunathan et al. 1999].

Another class of techniques for energy-efficient behavioral synthesis exploits control flow and locality of computation. Almost any real-life application does contain some control flow. Control flow forces mutual exclusion in computation and unequal execution frequencies that can be exploited to reduce power consumption. If we evaluate a conditional before we start the execution of its branches, we can easily detect idleness in functional units that execute operations in the branch that is not taken only. When idleness is detected early enough, we can eliminate switching activity by freezing (with clock gating or similar techniques) the idle units [Monteiro et al. 1996]. We can push this concept even further. If by profiling and control-flow analysis, we can determine the most frequently executed sections of a specification (i.e., the computational kernels), we can optimize the circuit for the common cases, provided that, at execution time, we can detect the occurrence of the common cases early enough [Lakshminarayana et al. 1999].

Example 4.4 Consider the simple code fragment shown in Figure 11(a). Assume that the profiling analysis has revealed that most of the time the value of c is 2. We can then transform the original code into the equivalent form shown in Figure 11(b). At a first sight, the second form is less compact and redundant. However, observe that in the new specification the branch of the conditional that executes more frequently contains just a shift operation that is much more power efficient than multiplication and subtraction, as needed in the infrequent path. Hence, by testing the condition c=2, we can disable the circuitry implementing the general computation, and just perform the power-efficient common-case computation.

```

while (c > 0) {

A = A * c;

c--;

while (c > 0) {

else {

while (c > 0) {

A = A * c--;

c--;

}

}

(a)

```

Fig. 11. Common-case computation and exploitation of mutual exclusion.

Optimization that is based on mutual exclusion and the common case often has area overhead because both methods limit hardware sharing. Hence, they can be counterproductive if the circuit operates with input patterns that completely change the probability distribution of the statements in the specification.

Application-specific processors. Even though dedicated computation units are very energy efficient, they completely lack flexibility. In many system design environments, flexibility is a primary requirement, either because initial specifications are incomplete or because they change over time. Also, many systems are designed to be reprogrammable in the field. Computation units for these systems must be programmable to some degree.