National Research University of Information Technologies, Mechahics and Optics Computer Technologies Department

# Michael Lukin, Sergey Velder, Anatoly Shalyto, Bulat Yaminov

**Verification of automata-based programs**

St.Petersburg 2011

# Contents

| Preface                                                         | 3  |

|-----------------------------------------------------------------|----|

| Chapter 1. Validation of systems                                | 6  |

| 1.1. Validation of systems tasks                                | 6  |

| 1.2. Simulation                                                 | 9  |

| 1.3. Testing                                                    | 9  |

| 1.4. Formal verification                                        | 12 |

| 1.5. Model checking                                             | 18 |

| 1.6. Automatic theorem proving                                  | 23 |

| Section 2. The mathematical apparatus of model<br>2.1. Modeling | 25 |

| 2.2. Model checking for linear temporal logic                   | 26 |

| 2.2.1. LTL Syntax                                               | 26 |

| 2.2.2. LTL Semantics                                            |    |

| 2.2.3. Verification of <i>LTL</i> using <i>Buchi</i> automata   |    |

| 2.3. Model checking for branching temporal logic                |    |

| 2.3.1. <i>CTL</i> syntax                                        |    |

| 2.5.2. C1 D semantics                                           | 57 |

| Section 3. Verificators overview                                | 39 |

| 3.1. SPIN                                                       | 39 |

| 3.2. SMV                                                        | 44 |

| Section 4. Verification of automata-based programs              | 47 |

| 4.1. Automata-based programs                                    |    |

| 4.2. Existing products abstract                                 |    |

| 4.3. Tools and subjects of verification                         |    |

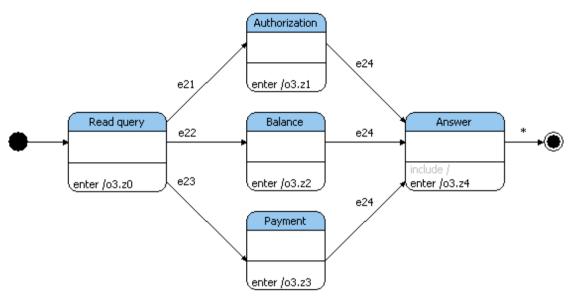

| 4.3.1. Automatic teller machine model                           |    |

| 4.3.2. Properties of ATM to verify                              | 57 |

| 4.4. Tools utilizing existing verifiers                         | 58 |

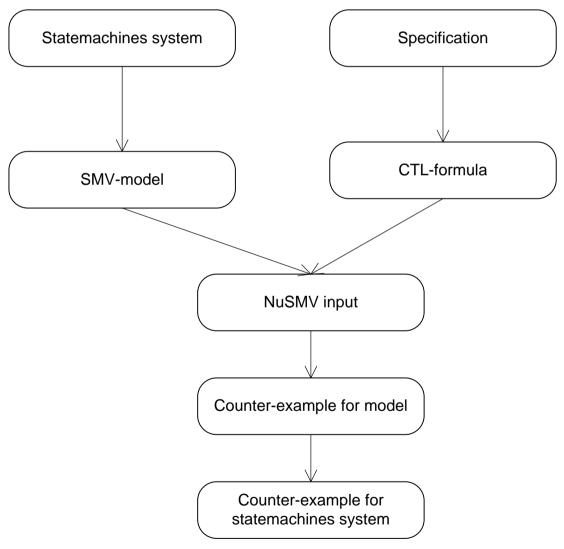

| 4.4.1. Converter                                                |    |

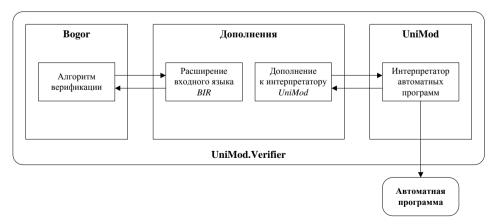

| 4.4.2. Unimod.Verifier                                          |    |

| 4.4.3. FSM Verifier                                             |    |

| 4.5. Autonomous verifiers                                       |    |

| <b>4.5.1.</b> <i>CTL Verifier</i>                               |    |

| ·                                                               |    |

| Conclusion                                                      | 92 |

| Bibliography                                                    | 94 |

# Preface

#### Validation concept

In everyday life information technology are increasingly used both directly (by using computers and internet) and indirectly (by using TV, microwaves, mobile phones, cars, public transport etc). In 1995 it was estimated that a person interacts daily with 25 devices processing information. We also know that 20% of the cost of developing vehicles, trains and planes account for computer components. Due to the high integration of information technologies to all applications we have to increasingly rely on the reliability of software and hardware. It is natural to assume that there must not be situations when the phone is faulty or when the VCR is unpredictable and incorrectly responds to commands sent from the control panel. Nevertheless, these errors are in a certain sense insignificant. However, errors in systems that are critical for safety, such as, for example, nuclear power or flight control systems are not acceptable. The main problem for such systems is that their complexity is rapidly increasing and, consequently, the number of possible errors.

Even if we ignore the aspects of security, errors can still be very expensive, especially if they occur after the product is released to the market. There are several striking examples of such adverse effects. For example, the error in the team division of floating point numbers in the Intel *Pentium* caused damage of about \$ 500 million. Major damage was caused by the crash of *Ariane-5* rocket, which probably occurred due to an error in the flight control program.

Therefore, validation of the systems (the process of validation of specifications, design and product) is an activity increasingly important. Validation is a way to maintain the quality control systems.

Of particular importance is ensuring the quality of software. Modern programming practice shows that the systems are checked by people (expert analysis) and dynamic testing. Support of these processes, even by relatively simple tools, not to mention the methods and tools with the serious mathematical base, is currently imperfect.

In view of the increasing size and complexity of systems, it is important to ensure the validation process systems using techniques and tools that facilitate the automatic analysis of correctness, as, for example, manual verification can be as inaccurate as the program itself.

#### Methods of validation systems

The most important methods of validation are expert analysis, testing, simulation, formal verification and validation of models. Will focus on two of them.

Testing is an effective way to verify that a given implementation of a system fit to the abstract specification. Testing can only be used after the implementation of the prototype system.

Formal verification, as opposed to testing is based on a mathematical proof of the correctness of programs.

Both of these methods can be supported and partially supported by the tools. For example, in testing there is a growing interest in developing algorithms and software for automatic generation and selection of tests on a formal specification of the system. The basis for formal verification is a program for automated theorem proof and test evidence, but even their use usually requires highly skilled users.

#### Model checking

The book covers a different validation method: model checking. This is an automated method which for a given model of system behavior with a finite number of states and logical properties, recorded in a suitable logical formalism (usually in the temporal logic), checks the validity of this property in this model. Model checking can be used to verify both hardware and software. The success of a number of projects using this method of verification increases the interest in it. For example, Intel has launched several research laboratories verification of new chips. An interesting aspect of model checking is that it supports partial verification: the system can be tested by a partial specification when considering only a subset of all claims.

#### The subject of the book review

The book is dedicated to the concepts, algorithms and tools for model checking software.

Ideas of testing models have such mathematical foundation as logic, automata theory, data structures, algorithms on graphs.

The book is structured as follows. The first chapter is about general issues of validation of software systems. We consider the formulation of the problem of validation and define the role of validation in software. Also different types of validation are distinguished, the basic concepts and definitions for each of them are given.

The second chapter outlines the theoretical issues of model checking, we introduce the different formalisms of temporal logics and model checking algorithms are described for the specifications expressed in these temporal logics. There are two types of models: *Kripke* models and *Petri* nets. Also some mathematical results concerning the properties of these models are presented.

Three types of test models are described: for linear and branching temporal logics and temporal logic for real-time. The first two capture the functional and qualitative aspects of the system, and the third is also to conduct a quantitative analysis.

The third chapter demonstrates the model-checking algorithms on examples of specific tools. A short description of the syntax of these tools and examples of the implementation of communication algorithms are given. Also there are results of testing models of these algorithms.

The presentation of general issues validation, the mathematical formalism and examples of verification models in first three chapters are according to a course of lectures of P. Cato [1].

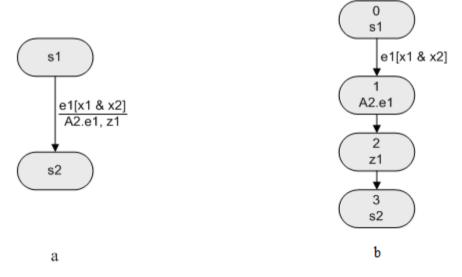

The fourth chapter is devoted to the verification of program models that are based on automata approach [2]. The main feature of these programs is that the model behavior of the program, presented as a system of control automata state for which code is generated, is built by the developer already at the design stage, rather than on the final program, as proposed to do with the traditional method of using model checking. These programs come in line with other engineering developments (such as airplanes and cars), for which the models are first created, and then based on them goods are manufactured, and not vice versa.

This edition is a translation of the main sections, made by M. Lukin, a monograph by the same authors with the same name, which is published by the publishing house "Nauka", Saint-Petersburg in 2011.

# **Chapter 1. Validation of systems**

## **1.1. Validation of systems tasks**

#### Introduction and motivation

The systems which are connected with the information processing more and more often provide critical services. They are used in a some conditions when failure could lead to the fatal consequences. Information processing widely used in such systems as nuclear power plant or chemical reactors. In these systems the errors are very dangerous. Another example of widelydistributed systems which are critical to safety is irradiative medical gadget.

So we could say that robustness and safety of information processing is a key factor in these systems.

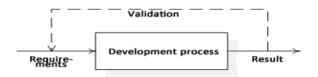

How can we ensure safety of program systems? Usually program development begins from analisys of the acceptance criteria. After passing of several development phases the prototype is come out. Validation is the process of evaluating software during or at the end of the development process to determine whether it satisfies specified requirements. In a diagram form the strategy of validation strategy is represented in fig. 1.1 [1].

Fig. 1.1. Schematic view of posterior validation

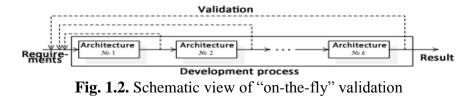

What is the general practice solution to the question when to validate? Clearly that the error checking only in the end of the development is not acceptable: if an error is found, required a lot of effort to fix it, because the whole development process must be passed again, to see where and how the error could occur. Such operations are usually expensive. Therefore, it is advisable to validate "on the fly" – in the process of developing system, as it significantly reduces the cost of development. Schematically, this process is shown in Fig. 1.2.

In practice, in order to ensure that the final result actually does what was prescribed there are two methods: expert analysis and testing. Researching on development programs show that 80% of all projects use expert analysis. Expert analysis is a fully manual activity in which a prototype or its part is researched by a team of experts who were not involved in the development of the system components. Testing is an important method of validation to validate the received implementations. However, tests are usually generated manually, and there is little attention given to instrumental support.

Validation of system is an important step in their development: most of the projects spent more time and effort on validation than on development. Mistakes can be very expensive. For example, the error in the Denver baggage handling system delayed the opening of a new airport to nine months (expense - \$ 1.1 million per day).

#### Validation of the system as a part of development process

Interviews with specialists of a number of companies engaged in software development, has once again shown that the validation of systems must be integrated into the development process at an early stage. This is true, in particular, from an economic point of view, but now most of the errors are found during testing, where software modules are already composed and the whole system is studied.

#### **Formal methods**

For quality assurance of complex software systems it is required the use of modern methods and tools that support the validation process. The currently applied methods of validation are highly specialized and based on specifications formulated in natural language. Therefore, this book examines approaches to validation based on formal methods. When using such techniques design systems should be defined in terms exact and unambiguous specifications that provide the basis for systematic analysis. List the basic approaches to validation:

- 1. Simulation.

- 2. Testing.

- 3. Formal verification.

- 4. Model checking (verification on model).

Later we will briefly discuss the first three approaches, but the main theme, as noted above, is model checking.

#### **Reactive Systems**

This book focuses on the validation of reactive systems. *Reactive systems* are characterized by continuous interaction with the environment. They take the inputs from its environment and usually with little delay, react to them. Typical examples of this class of systems are operating systems, aircraft control systems, vehicles and processes, communication protocols, etc. For example, the control of chemical processes on a regular basis takes the control signals such as temperature and pressure at different points of the process. Based on this information, the program may decide to include a heating element, turn off the pump, etc. If you have a dangerous situation, for example, the pressure in the tank outside certain limits, the control program must perform certain actions. Typically, such reactive systems are quite complex.

As noted above, the correctness of reactive systems is crucial. To build a working rocket system correctly requires a clear methodology, which distinguishes the following phases.

- 1. On the basis of an exhaustive analysis of the requirements its specification should be formed.

- 2. Conceptual design gives an abstract specification of the project. This specification can be checked for consistency and compliance. This validation process can be supported by formal verification, simulation and model testing such processes, in which the model of an abstract design specification (for example, a system of state machines) can be exhaustively tested.

- 3. When a credible specification is obtained, move to a system that implements an abstract specification. In this testing is a useful method of checking the implementation for compliance original requirements.

## 1.2. Simulation

*Simulation* is based on a model that describes the possible behavior of the system. This model is feasible in a certain sense, while the software tool (called a *simulator*) can determine the system behavior in relation to some scenarios. In this way the user gets a certain understanding of how the system responds to stimulus. Scripts can be supplied by the user or a tool such as, for example, a generator, which constructs random scenarios. Simulation is mainly useful for rapid, initial assessment of project quality. It is not well suited to find subtle bugs as simulation of all possible scenarios is impractical (and frequently impossible).

## 1.3. Testing

As noted above, a widely used traditional way of validation of project correctness is testing [6]. In testing system used in the form in which it is implemented (program, device, or combination of them). Certain values of the input data, called tests are served to its entrance, and the response of the system is studied. After it we check whether the response of the system corresponds to the required output. Principles of testing are almost the same as in the simulation. Their major difference lies in the fact that testing is done on the current system implementation, and simulation – on a model of system.

Testing is a validation method that is widely used in practice, but almost always performed on the basis of informal and heuristic methods. As testing is based on the consideration of only a small subset of possible examples of system behavior, it can never be complete. E. Dijkstra pointed out that testing can only show the presence of bugs but not their absence.

Testing, however, can complement the formal verification and validation of models that run on a mathematical model of the system rather than actual system. As the testing is used to realization it is useful mainly in the following cases:

- when the correct model of system is difficult to build;

- when parts of the system can not be formally modeled (for example, physical devices);

- when the model is proprietary.

Generally, testing is the dominant method of validation systems. It is applied to a number of tests that are normally received heuristically. In recent years,

however, an interest in the application of formal methods in testing is increasing. For example, in the field of communication protocols, this type of research has led to a draft international standard, "Formal methods in testing fitness". The testing process is divided into several phases:

- 1. Test generation. Abstract descriptions of the tests are generated systematically on the basis of exact and unequivocal set of properties required in the specification.

- 2. The choice of tests. The set of samples of abstract descriptions of the tests are chosen.

- 3. The implementation of tests. Abstract descriptions of the tests are transformed into executable tests.

- 4. Execution of tests. Executable tests are used to test the implementation by running them on a testing system. Considered and recorded the results of execution.

- 5. Test analysis. Logged results are analyzed to determine if they satisfy the expected results.

- 6. The different phases of testing can intersect and often intersect in practice, especially the last.

Testing is a method that can be used as prototypes in the form of systematic simulation, as well as to the final products. There are two known basic approaches: the white-box testing, when the internal structure of the implementation can be observed and sometimes partially controlled (stimulated), and black box testing. In the second case only communication between the test system and the environment can be verified, and the internal structure of the "box" is completely hidden from the tester. In practical circumstances, testing is somewhere between these two extremes, and sometimes is called as gray box testing.

List the main types of tests.

- 1. Unit tests. Test is written for a class, a separate method of this class, etc. Usually one script of using of class, method, or a module is checked.

- 2. Functional tests. Not an element of the code is testing but functionality. These tests make possible identifying structural errors.

- 3. Acceptance tests. Verified that the program does exactly what the customer wanted.

- 4. Stress Test. Operability testing program under heavy load.

- 5. Monkey Test. Program is served by the random input data, and its performance on such data and fault tolerance are tested. Vulnerabilities are also scanned for. Such tests are particularly important for server applications.

- 6. Parallel tests. Verified that the new version works just like the old one.

- 7. Regression tests. Written after the error message. The test repeats scenario in which the error occurred.

#### **Test-driven development**

One of the technologies of software development is test-driven development (TDD). Note that TDD is not a test technology. This process consists of short iterations of development of programs, each of which consists of the following steps:

- 1. Writing test.

- 2. Compilation of the test. The test should not be compiled. If the test is compiled, it means that you have created an entity that already exists.

- 3. Removing compilation errors.

- 4. Run the test. The test should fail.

- 5. Writing the code. Written as a simple code as only possible.

- 6. Run the test. This time the test should be passed.

- 7. Refactoring (if required).

The second and third steps are performed only after creating new modules or classes.

When the program uses the equipment which access is difficult to, mock objects are used or mocks. Mocks are automatically generated stubs. Mocks also can be used to top-down programming. To create a mock object frameworks, there are special (*RhinoMock, NMock, JMock,* etc.). Properties of development through testing:

- approach makes to develop the program from a user perspective;

- it makes writing classes, independent of each other;

- tests are also documentation to the code;

- it takes time to learn this approach in practice.

# **1.4. Formal verification**

Complementary method to the simulation and testing is a rigorous proof that the system is working correctly. Such mathematical demonstration of the correctness of the system is called *formal verification* [11]. The basic idea is to construct a formal (mathematical) model of the system, which reflects (specifies) the possible behavior of the system. The requirements of correctness are written as a formal requirement specification, which reflects the desired behavior of the system. Based on these two specifications using formal proof we can verify whether the possible behavior is consistent with the desired. As there is a verification of a mathematical form, the notion of consistency can be precise and verification consists in proving the correctness towards this formal representation.

For formal verification are required:

- System model, typically containing a set of states, which keep information about the values of variables, software counters, etc., and the ratio of transitions, which describes how the system moves from one state to another.

- Specification method for expressing requirements in a formal way.

- The set of rules of evidence, allowing determination of whether the model meet the formulated requirements.

In order to more precisely understand what is meant, consider the method by which sequential programs can be formally verified.

#### Verification of sequential algorithms

This approach can be used to prove the correctness of sequential algorithms [1, 12], such as quick sort or calculation of the greatest common divisor of two integers. It begins with the formalization of the desired behavior using pre-and postconditions based on predicate logic formulas. The syntax of these formulas can be determined, for example, as follows:

$$\varphi ::= p \mid \neg \varphi \mid (\varphi \lor \varphi).$$

Here p is basic proposal (for example, "x equals 2"), the symbol "¬" is denial, and the symbol " $\vee$ " is disjunction. Other logical connectives can be defined as follows:  $\varphi \land \psi = \neg(\neg \varphi \lor \neg \psi)$ , true =  $\varphi \lor \neg \varphi$ , false = ¬true and

$\varphi \rightarrow \psi = \neg \varphi \lor \psi$ . For simplicity, we omit the existential and universal quantifiers.

A precondition describes the set of starting conditions studied (valid values of inputs), and post-condition – the set of desired final states (the required values of the outputs). When pre-and postconditions are formalized, the algorithm is coded in an abstract pseudo-code, and step by step, we prove that it meets specifications.

To build the proof we use the *formal system* which is a set of *inference rules*. These rules are usually associated with program building (algorithm). They are written as follows:

$\{\varphi\} S \{\psi\}.$

Here,  $\phi$  is a precondition, S is a software operator and  $\psi$  is postcondition.

Triple { $\phi$ }, S, { $\psi$ } is known as the triple Hoare and named in honor of one of the pioneers in the field of formal verification of computer programs. There are two interpretations of Hoare triples, depending on whether partial or total correctness is considered.

- The formula  $\{\phi\}$  S  $\{\psi\}$  is called partially correct if each stopping calculation of S, starting in a state wherein  $\phi$  is running, finish in the state in which  $\psi$  is running.

- Formula  $\{\phi\}$  S  $\{\psi\}$  is called totally correct if every calculation of S, starting in a state in which  $\phi$  is running, stop and finish in the state in which  $\psi$  is running.

Thus, in the case of partial correctness we make no assumptions about the calculation of S, which did not stop and hang up. In further explanation the partial correctness is considered, if not stated otherwise.

The main idea of the approach of Hoare is to prove the correctness of programs at the syntactic level, using only the triples of determined above forms. Deterministic sequential programs are designed according to the following grammar:

S ::=**skip** | x := E | S; S | **if** B **then** S **else** S **fi** | **while** B **do** S **od**.

Here, skip is no operation, x = E is assignment expression E to variable x (we assume that x and E have the same type), S; S is a composition of operators. The last two are alternative and iteration, respectively (B is Boolean expression).

The rules of inference should be read as follows: if all conditions located above the line are true, then the corollary under the dash is also true. For rules with a condition it is necessary to write only the result. These inference rules are called axioms. A formal system for sequential deterministic programs is shown in table 1.1.

| Axiom for skip        | $\{arphi\}$ skip $\{arphi\}$                                   |

|-----------------------|----------------------------------------------------------------|

| Axiom for assignment  | {cfex=+{]}x=+<{c}                                              |

| Sequental composition | <u></u>                                                        |

| Altenative            | EPSSE PSSE                                                     |

| Iteration             | EPBSB<br>ESHERISE                                              |

| Consequence           | <del>\$\$\$\$</del> \$\$\$\$\$\$\$\$\$\$\$\$<br>{}\$\$\$\$\$\$ |

Table 1.1. Formal system for partial correctness of sequential programs

Inference rule for the operator skip, which does nothing, is quite expected: in all conditions, if  $\varphi$  is true before the operator, it is also true after it. According to the axiom for the assignment, start with the postcondition  $\varphi$ and define the precondition by substituting  $\varphi$  [x: = k]. This substitution means formula  $\varphi$ , in which all occurrences x are replaced by k.

#### For example:

$$\{k2 \text{ is even and } k = y\} x := k \{x2 \text{ is even and } x = y\}.$$

If the proof process begins with an analysis of post-conditions, it is usually used in series to parts of the program so that in the end we can prove the precondition for the program.

The rule of the sequential composition uses intermediate predicate  $\chi$ , which characterizes the final state of the  $S_1$  and the initial condition  $S_2$ . The rule of alternative uses a boolean expression B, whose value determines what exactly is executed:  $S_1$  or  $S_2$ .

The rule for iteration requires explanation. It determines that predicate  $\varphi$  is performed after the end of "while B do S od", if the validity of  $\varphi$  can be maintained during the each execution of the loop body S. This explains why  $\varphi$  is *invariant*. One major difficulty in proving the correctness of programs using this approach consists in finding suitable invariants. In particular, this complicates the automation of such proofs.

All the rules are focused on such syntax that to each syntactic construction corresponds rule of inference. This is different from the rules of the investigation, which establishes a link between verification of programs and logic.

The rule of investigation allows to increase precondition and weaken postcondition. At the same time it facilitates the application of other rules. In particular, this rule allows you to replace the pre-and post-conditions to equivalent ones. However, it should be noted that the proof of the implication of the form  $\varphi \Rightarrow \varphi'$  in general is undecidable. Now let us discuss the total correctness. Proof system in table 1.1. is not enough to prove that the sequential program stops. The only syntax, which can lead to crashes (not stopping) calculations is iteration. To prove the presence of the halt the inference rule for the iteration can be improved as follows:

Here, an auxiliary variable N is not included in  $\varphi$ , B, n or S. The meaning of this rule lies in the fact that N is the starting value of n, and at each iteration, the n value decreases, but remains non-negative. This construction eliminates the endless calculations because n can not decrease infinitely often without violating the condition  $n \ge 0$ . The variable n is called a variant.

#### Formal verification of parallel systems

Suppose that for the operators  $S_1$  and  $S_2$  structure  $S_1 || S_2$  means parallel composition of these operators. The main application for formal verification of parallel programs is the following inference rule:

#### &\$\${\varbox} {&\$\$\$

This rule allows to verify the parallel systems in the same way as a consistent, considering the parts of a program separately. Due to the interaction between  $S_1$  and  $S_2$ , at least through access to shared variables or message exchange, this rule is, unfortunately, is false in general. Many efforts have been made to obtain inference rules of a described form. There are several reasons why this is not easy to achieve.

The insertion of parallelism leads to the insertion of nondeterminism. This means that for parallel programs that communicate using shared variables, the behavior of the input-output depends on the order in which these shared variables are accessed.

For example, if  $S_1$  is x := x + 2,  $S_2$  is x := x + 1; x := x + 1 and  $S_3$  is x := 0, value of x after  $S_1 || S_3$  can be 0 or 2, and value of x after  $S_2 || S_3$  can be 0, 1 or 2. Different values of x depend on the order executing statements in the  $S_1$  and  $S_3$  or  $S_3$  and  $S_3$ . Moreover, despite the fact that the input-output behavior  $S_1$  and  $S_2$  is identical (increase x in 2), there is no guarantee that this will be true in a parallel context.

Parallel processes can potentially interact at any point of their performance, not just at the beginning of the calculation. If you want to make a conclusion about how parallel programs interact, it is not enough to know the properties of their starting and final states. It is also necessary to be able to form judgments about what happens during the computation. Thus, the properties must refer not only to the starting and final states, but also on the calculations themselves.

The main problem of the classical approach to the verification of concurrent and reactive systems is that, as explained above, that verification is fully focused on the idea of how the program computes the function from inputs to outputs. At the same time some valid inputs are given and desired outputs are produced. For parallel systems calculation is usually not complete, and correctness depends on the behavior of the system over time, and not only from the final calculation result (if it ever ends). Global properties of parallel programs often can not be formulated in terms of relations between inputs and outputs.

Various attempts have been made to generalize the classical formal verification of concurrent programs. Due to the interaction between the components the rules of inference are usually quite complex, and full development of a formal system for parallel systems that can communicate using shared variables or by (synchronous or asynchronous) messaging becomes difficult. Therefore, for real systems, proving in this style is usually very large and complex. It is required to consider user interaction and control from it (in particular, in the form of finding suitable invariants). As a result, such proof is very cumbersome, resistant to bugs, and arrange them in an understandable manner is difficult.

#### **Temporal logic**

As noted above, the correctness of reactive systems is considered in relation to the behavior of systems during the time, not only to the relationship between inputs and outputs (pre-and post conditions) calculations, since the calculation of reactive systems is usually not complete. Consider, for example, the communication protocol between two agents (a sender and a receiver), which are connected by two-way communication channel. In this case, the property "If the process P sends a message he would not send the next message until confirmation will be received" can not be formulated in terms of pre-and postconditions.

In order to facilitate the formal specification of such properties, propositional logic should be extended by operators that refer to the behavior of the system over time. U (until) and G (globally) – are examples of statements that refer to a sequence of states (such as, for example, calculations). In this case  $\phi \cup \psi$  means that the property  $\phi$  is performed in all states until you reach a state in which the  $\psi$  is performed, and G  $\phi$  means that always, in all future states  $\phi$  is performed. Using these operators, we can formalize the above-described property of protocol, for example, as follows:

**G** [

$$snd_P(m) \rightarrow \neg snd_P(nxt(m))$$

**U**  $rcv_P(ack)$ ].

In other words, if a message m is sent by process P, then this process does not transmit the following message nxt (m), until it receives confirmation.

Logics, advanced by operators, which allow to express properties of computation (in particular, that can express properties of mutual order between events), are called temporal logic. These logic in computer science were introduced by Pnueli [15, 16]. Temporal logic is a widely used method of specification for expressing properties of computing of reactive systems at a rather high level of abstraction.

In the same way as in the verification of sequential programs, we can construct inference rules for temporal logic (for reactive systems), and prove the correctness of these systems by the same approach as was shown for sequential programs using predicates. Disadvantages of the method of verification of proof, which requires a great deal of human labor, the same as checking for parallel systems: proof is bulky, cumbersome and requires a high level of user control.

This book show a different type of formal verification method, which is based on temporal logic, but, in general, requires less user involvement in the verification process. It is called *model checking*.

## 1.5. Model checking

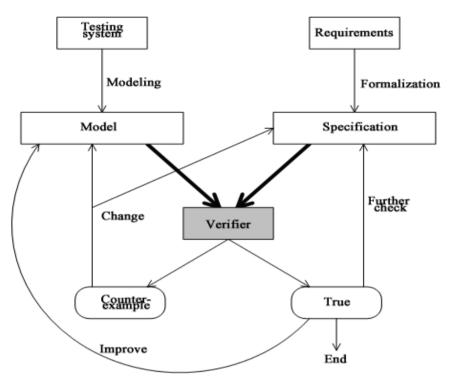

The main idea of the method, called model checking [1, 17, 18], is to run the algorithms executed by the computer to check the correctness of systems. Using this approach, the user enters a description of the model system (possible behavior) and a description of the specification requirements (desired behavior), and machine holds the verification. If an error is found, the tool (verifier) provides a counterexample showing that under what circumstances the error can be detected. A counterexample is a scenario in which the model behaves in an undesirable way. He indicates that the model is not valid and should be corrected. This allows the user to detect the error and correct model specification before continuing verification. If no errors are found, the verification can be completed or the user can specify the model (taking into account more design decisions, so that the model becomes more concrete and realistic) and repeat the verification process. The scheme of model checking is shown in Fig. 1.3.

Fig. 1.3. Model checking

Algorithms for testing models are usually based on an exhaustive review of the set of all states of the model system: for each state of the system is checked, "Does it behave correctly" – satisfies a required property. In the simplest form, this method is known as attainability analysis. For example, suppose it is required to find out whether the system can reach a state in which the computation can not continue (so-called blocking). In this case, is sufficient to determine all the attainable states and determine whether there is an attainable state in which the computation is blocked. Attainability analysis is applicable only to prove the absence of locks and invariant properties that are performed during the whole computation. This is not enough, for example, for communication protocols, for which one of the important properties is the following: if the message is sent, it must ever be received. These types of properties are not covered by standard test of feasibility.

Protocols are modeled by sets of finite state machines that communicate by asynchronous message exchange [19]. Starting from the initial state of the system, which is expressed in terms of states of interacting automata and message buffers, all the states of the system are determined, which can be achieved by exchanging messages. Model checking can be considered as the

successor to these early methods of review of all states for protocols. It allows you to check a wider class of properties and manages a set of states much more effective than earlier methods.

#### Methods of model checking

There are two known approaches of model checking. They differ in how to describe the desired behavior which is a specification of requirements.

*Logical or mixed approach.* In this case, the desired system behavior is described by the language of numerous properties in a suitable logic (temporal or modal). The system is usually modeled as a finite state machine, in which states reflect variables and control positions, and transitions indicate how system could change one state to another. The system is correct in relation to requirements if the given set of initial states fulfills these requirements.

*Behavioral or uniform approach.* In this case both desirable and possible behaviors are defined in the same notation (machine), and as a criterion for the correctness equivalence relations are used (or pre-orders). Equivalence relations usually fix representation of the form "behaves like", while the preorder relations indicate the submission of the form "behaves at least like". As there are different views about what it means for two processes "behave the same way" (or "to at least like"), it defines various notions of equivalence and preorder. One of the most well-known concepts of equivalence is a double modeling, in which the two machines model each other, if one machine can simulate every step of the other machine and vice versa. Frequent presentation of pre-order is the inclusion of languages. The automata A is included in the automata B, if all the words allowable by A, shall also be permitted by B. The system is considered correct if desired and possible behavior are equivalent (or ordered) in relation to studied equivalence (or preorder).

Despite the fact that both of these approaches are conceptually different, connection between them can be set as follows. Logic induces an equivalence relation on systems like this: two systems are equivalent if and only if they satisfy the same formulas. Using this concept, we can establish the relationship between logic and equivalence relations. For example, we know that two machines model each other if they satisfy the same formulas of the logic *CTL*, widely used in the process of model checking. The

relationship between the two approaches is clear now: if two models satisfy the same properties (this is checked using a logical approach), they are behaviorally equivalent (this can be checked using a behavioral approach). The backward path is more interesting, as is generally impractical to inspect all properties in a certain logic, but verification of equivalences, such as dual modeling can be done efficiently.

This book uses logical approach [20]. Since there is essentially verified that the description of the system is a model of temporal logic formulas, this logical approach is originally called model checking. An exhaustive review of the set of states guaranteed end because of the finiteness of the model.

#### The advantages of model-checking

- This is a common approach with applications to verification of hardware, software, communication protocols, multi-agent systems, embedded systems, etc.

- Approach supports partial verification: the project can be verified by a partial specification when considering only a subset of all claims. This approach provides a high efficiency because you can limit the validation test of the most important properties while ignoring the less important test, but computationally more expensive claims.

- Inlining test patterns into the design process does not require more time than the simulation and testing. In some cases the use of model-checking leads to a reduction of development time. In addition, the use of appropriate methods, model checking programs can work with rather large state spaces.

- Program to test the models could potentially be used regularly by specialists in systems development with the same ease with which used, for example, compilers, as model checking does not require a high degree of user interaction.

- Reliable mathematical basis: modeling, semantics, logic and automata theory, data structures, algorithms on graphs.

#### Limitations of model checking

The major limitations of model checking:

- It applies mainly to the management applications, in which the components interact with each other. It is less suited to data applications as well as in such applications infinite state spaces are usually introduced.

- When using the model checking only the model of the system is verified, not the system itself. The fact that the model has certain properties, does not guarantee that the final implementation will have the same properties (to verify the final implementation additional methods such as systematic testing are needed). Simply put, any validation using model checking is as good as the model system.

- Finding a suitable abstraction (such as a model system, and suitable properties in temporal logic) requires appropriate qualification (but less than evidence-based verification).

- Like any tool, software for model checking can be unreliable. However, as the basis for model checking are standard and wellknown algorithms, the reliability of such programs is usually no big problem. In some cases, the correctness of the most difficult parts of the software model checking has been proved with the use of automatic theorem proving programs.

- Model checking does not allow to verify the generalizations. If, for example, the protocol is verified for one, two and three processes using model checking, it does not give any result for a different number of processes. Model checking is practical only for special cases. Model checking, however, can help to formulate the theorem with arbitrary parameters, which can later be proven using formal verification.

It is impossible to reach absolutely guaranteed correctness of systems of real-size. Despite these limitations, we can say that model checking greatly increases the level of confidence in systems.

As in model checking the basic idea is to describe the behavior of the system by finite automata, under certain conditions, the number of states can go beyond the size of available memory. This, in particular, may be for parallel and distributed systems in which there are many system states. The size of the set of states of such systems in the worst case is proportional to the product of the sizes of the sets of states of individual components. The problem of excessive increase in the number of states is called the combinatorial explosion problem [17]. As shown below, the use of automata-based programming [2] allows you to look at this problem from another point of view.

## **1.6.** Automatic theorem proving

Automatic theorem proving can be used effectively in areas where mathematical abstractions of tasks are available. For the case of validation systems specification and realization of system are regarded as formulas, for example,  $\varphi$  and  $\psi$ , written in a certain logic. The checking that the implementation satisfies the specification reduces to checking formulas  $\psi \rightarrow \varphi$ . This means that behavior of implementation that satisfies  $\psi$ , is a possible behavior of the system specification, and therefore satisfies  $\varphi$ . Note that the specification of the system can allow other behavior that is not realized. To prove  $\psi \rightarrow \varphi$  programs of automatic theorem proving are used.

Verification of the proof is an area closely related to the proof of theorems. User can send proof of theorem to the program to check the evidence. Software responds whether that proof is true. Programs of verification of evidence do a simpler problem than programs of automatic theorem proof. with complicated Therefore. they can work proofs. more In order to reduce the amount of search in proof theorems, it makes sense to interact with the user, who may be knowledgeable about the best strategy for constructing a proof. Usually such interactive systems help in searching for evidence by maintaining a list of actions that need to be done, and provide clues how yet not proved theorems can be proved. Moreover, every step of the proof is verified by the system. As a rule, for evidence it must be made a lot of small steps, and high level of user interaction is required. Usually people overlook small parts of the evidence ("trivial", "same"), while the program requires an explicit presence of these parts. The verification process using the automatic theorem proof software is slow and laborious. In addition, the using instruments typically require quite high qualification of users.

The logic used by programs of proof theorems and programs of test evidence, usually is a variant of first-order predicate logic. In this logic there is an unlimited set of variables, the set of functional and predicate symbols of specified ary. Ary indicates the number of arguments of the functional or predicate symbol. Term is a variable or a string of the form  $f(t_1, ..., t_n)$ ,

where *f* is a function symbol of ary, n and  $t_i$  are terms. Constants can be considered as a function of ary 0. Predicate has the form *P* (*t*1, ..., *tn*), where P is a predicate symbol of ary n, and  $t_i$  – terms.

Propositions of first-order logic are predicates, logical combinations of proposal or proposals, provided with quantification of the existence or universality. In a typed logic, there are also many types, and each variable has a type (as a program variable x has type int). Each function symbol has a lot of argument types and result type, and each predicate symbol has many types of arguments, but not the type of result. For this reason, in this logic, quantifications are also typed.

Algorithmic components of programs of proof theorems are the methods of application inference rules and the consequences of receiving. Important approaches used by programs for this are a natural deduction (e.g., if  $\varphi 1$  and  $\varphi 2$  are true we can conclude that  $\varphi_1 \wedge \varphi_2$  are also true), resolution and unification (a procedure that is used for comparing two terms with each other by providing all permutations of the variables in which terms are the same). In contrast to traditional model checking, theorem proof can work directly with infinite sets of states and check the validity of properties with arbitrary values of the parameters.

These methods are not sufficient to find the evidence of given theorem, if the evidence exists. The tool should have a strategy that says how to find evidence. This strategy may offer the using of inference rules from the end, starting with the proposal, which is required to prove. The strategies that people use to find evidence are not formalized. Strategies used by programs proofs of theorems are based on the traversal algorithm in width and in depth.

Finally, programs of proving theorems are not very useful in practice: the problem of proving of theorems is exponentially complex. Sentence of length n can have a proof of exponential size of n. Searching for this proof requires exponential time on its length. Therefore, in general, theorem proof is double exponentially in relation to the length of proof proposition. For interactive programs of theorem proving, this complexity is greatly reduced.

List the differences between theorem proving and model checking:

• Model checking is fully automatic and fast.

- Model checking can be applied to partial implementations. Therefore, it can provide useful information about correctness of the system even if the system is not fully defined.

- Model checking programs have user-friendly interface and are easy to use, while the use of software test evidence requires a rather high qualification of the users in order to guide and accompany the process of verification. In particular, it is difficult to introduce someone to the logical language of program proving of theorems, which is usually the expressive logic of higher order.

- Model checking is useful to management applications, such as reactive systems. Proving of the theorems is applicable to work with infinite sets of states, and therefore it can be used for data processing applications.

- In case of success proving of theorems gives (almost) the highest level of accuracy and reliability of the evidence.

- Model checking can generate counterexamples that can be used to assist in debugging.

- When using the model checking, the project is checked for a fixed (and finite) set of parameters. The using of programs of proving theorems is possible for arbitrary values of the parameters.

Model checking is not considered as a "best" approach compared with the proving of theorems. These methods complement each other because each of them has certain advantages. Attempts were made to integrate these methods in order to get the effect of combining the advantages of both approaches.

# Section 2. The mathematical apparatus of model 2.1. Modeling

Model checking method does not work with program directly. It works with model of program. In this section is described how to create model.

At first the specification for the program is created. So long as model checking method works with model, the model must have all the properties which are described in the specification. However inessential details are not needed. For instance if in the specification of lift control system described that the lift doors must be closed in time of moving, then speed of lift is inessential.

In this book the most interesting systems are reactive systems [17]. These systems can not be modeled in terms of input-output because they can work indefinitely long. So for these systems their time behavior is verified. For this the notion *state of the system* is introduced. State of the system is its instant description with fixed values of all variables in the system. Work of reactive system can be imagined as transitions between states.

Formally we can represent work of this system as Kripke model [17].

Firstly introduce the notion of *set of atomic propositions*. *Atomic proposition* is a proposition such that inner structure can not change. Atomic propositions are basic propositions. Set of atomic propositions is denoted by *AP*.

Examples of atomic propositions:

- "x > 0"

- "x = 5"

*Kripke model* over the set of atomic propositions *AP* is a triple (*S*, *R*, *Label*) such that:

- *S* is a nonvoid set of states;

- $R \subseteq S \times S$  is a *total transitions relation* on *S*, which associates an element  $s \in S$  the set of its possible successors;

- Label:  $S \rightarrow 2^{AP}$  associates each state  $s \in S$  atomic propositions Label(s), that are true in s.

Relation  $R \subseteq S \times S$  is *total*, if it associates each state  $s \in S$  at least one successor ( $\forall s \in S: \exists s' \in S: (s, s') \in R$ ).

# 2.2. Model checking for linear temporal logic

#### 2.2.1. LTL Syntax

Following definition defines set of basic formulae which can be expressed in linear temporal logic (*LTL*).

Let *AP* is set of atomic propositions. Then:

1. *p* is formula for each  $p \in AP$ .

- 2. If  $\varphi$  is formula, then  $\neg \varphi$  is formula.

- 3. If  $\varphi$  and  $\psi$  are formulae, then  $\varphi \lor \psi$  is formula.

- 4. If  $\varphi$  is formula, then **X**  $\varphi$  is formula.

- 5. If  $\varphi$  and  $\psi$  are formulae, then  $\varphi \mathbf{U} \psi$  is formula.

Set of formulae constructed using these rules is called LTL formulae.

Note: set of formulae that constructed using the three first rules defines set of all propositional logic formulae. Therefore propositional logic is a subset of *LTL*.

The LTL syntax can be defined in Backus-Naur form:

$\varphi ::= p \mid \neg \varphi \mid (\varphi \lor \varphi) \mid \mathbf{X} \varphi \mid (\varphi \mathbf{U} \varphi).$

Logical operators satisfy the following:

$$\begin{split} \varphi \wedge \psi &= \neg (\neg \varphi \vee \neg \psi), \\ \varphi \to \psi &= \neg \varphi \vee \psi, \\ \varphi \leftrightarrow \psi &= (\varphi \to \psi) \wedge (\psi \to \varphi). \end{split}$$

*true* equals  $\varphi \lor \neg \varphi$ , *false* equals  $\neg true$ . Temporal operators **G** (Globally, "always") and **F** (Future, "some time in future") by definition put:

$$\mathbf{F} \ \varphi = true \ \mathbf{U} \ \varphi,$$

$$\mathbf{G} \ \varphi = \neg \mathbf{F} \ \neg \varphi.$$

All the states satisfy *true* therefore  $\mathbf{F} \varphi$  means that  $\varphi$  come true some time in future.  $\mathbf{G} \varphi$  means that "it is wrong that some time in future  $\neg \varphi$  come true". Therefore it means that  $\varphi$  always is true.

#### 2.2.2. LTL Semantics

Shown above definition gives a method to construct *LTL* formulae but does not give an interpretation. Formally **X**  $\varphi$  means that  $\varphi$  is *true* in the next state, **F**  $\varphi$  means that  $\varphi$  will be *true* (now or in some moment in future). But what do the words "state", "next state" and "some moment in future" means? The formal interpretation (it usually called semantics) helps us unambiguously determine these terms. The formal meaning of properties in temporal logic is defined in terms of *model*.

**Definition**. *LTL-model* is a triple M = (S, R, Label) such that:

- 1. *S* is a nonvoid set of states;

- 2.  $R: S \rightarrow S$  maps the state  $s \in S$  the single next state R(s) (next function).

- 3. Label:  $S \rightarrow 2^{AP}$  maps each state  $s \in S$  atomic propositions Label(s), which are true in s.

**Example**. Let  $AP = \{x = 0, x = 1, x \neq 0\}$  is a set of atomic propositions,  $S = \{s_0, ..., s_3\}$  is a set of states,  $R(s_i) = s_{i+1}$  for  $0 \le i < 3 \bowtie R(s_3) = s_3$  is a next function and  $Label(s_0) = \{x \neq 0\}$ ,  $Label(s_1) = Label(s_2) = \{x = 0\}$ ,  $Label(s_3) = \{x = 1, x \neq 0\}$  is a label function. In the model M = (S, R, Label) the atomic proposition "x = 0" is true only in states  $s_1$  and  $s_2$ , the atomic proposition " $x \neq 0$ " is true only in states  $s_0$  and  $s_3$ , the atomic proposition "x = 1" is true only in state  $s_3$ .

The meaning of formulae in logic is defined in terms of *formula* satisfiability relation. Let be formula satisfiability relation.

Formula satisfiability relation means that  $M, s \models \varphi$  if and only if когда  $\varphi$  is true in the state *s* of the model *M*. When the model *M* is obvious from the context, we will write  $s \models \varphi$  instead of *M*,  $s \models \varphi$ .

Define LTL semantics. Let  $R^{0}(s) = s$ ,  $R^{n+1}(s) = R(R^{n}(s))$  for each  $n \ge 0$ . Let  $p \in AP$  is atomic proposition, M = (S, R, Label) is *LTL* model,  $s \in S$  and  $\varphi, \psi$  are *LTL* formulae. By definition, put

$$s \models p \qquad \Leftrightarrow p \in Label(s);$$

$$s \models \neg \varphi \qquad \Leftrightarrow \neg (s \models \varphi);$$

$$s \models (\varphi \lor \psi) \qquad \Leftrightarrow (s \models \varphi) \lor (s \models \psi);$$

$$s \models \mathbf{X} \varphi \qquad \Leftrightarrow R(s) \models \varphi;$$

$$s \models (\varphi \mathbf{U} \psi) \qquad \Leftrightarrow \exists j \ge 0; R^{j}(s) \models \psi \land (\forall 0 \le k < j; R^{k}(s) \models \varphi).$$

For instance, consider semantics of  $\mathbf{F} \varphi$ .

$$s \models \mathbf{F} \varphi$$

$\Leftrightarrow$  {by definition of **F**}

$s \models true \mathbf{U} \varphi$

$\Leftrightarrow$  {semantics **U**}

$$\exists j \ge 0: R^{j}(s) \models \varphi \land (\forall 0 \le k < j: R^{k}(s) \models \text{true})$$

$\Leftrightarrow \{\text{simplify}\}$

$\exists j \ge 0: R^{j}(s) \models \varphi.$

Therefore  $\mathbf{F} \varphi$  is true in the state *s* if and only if there is exists one of next states such that  $\varphi$  is true in that state or  $\varphi$  is true in the state *s*.

#### Model checking and satisfiability

In the first section the informal definition of model checking problem was given. Now we can give the formal definition:

Suppose the finite model *M*, the state *s* and the formula  $\varphi$ . Is *M*, *s*  $\models \varphi$  true?

The task of model checking should not be confused with the more traditional problem of the satisfiability in logic. *Satisfiability problem* can be formulated as follows:

Suppose the property  $\varphi$ . Do exist the model *M* and the state *s* such that  $M, s \models \varphi$ ?

The satisfiability problem for *LTL* is solvable. Therefore the model checking problem is solvable too.

#### 2.2.3. Verification of LTL using Buchi automata

There are several methods to represent *LTL* formula as transitional graph for model checking. One of this methods uses *Buchi automata*.

Let *AP* is a set of atomic propositions. The *Buchi automaton over the* alphabet  $2^{AP}$  is the quadruple  $A = (Q, q_0, \delta, F)$  such that

- *Q* is a finite set of states;

- $q_0$  is the start state;

- $\delta \subseteq Q \times 2^{AP} \times Q$  is a total transition relation;

- $F \subseteq Q$  is a set of accept states.

We describe the algorithm due to Gerth, Peled, Vardi and Wolper [16, 17] for constructing a *Buchi* automaton from *LTL* formula.

Let  $\mathbf{R}$  (Release) be a temporal operator such that

$\varphi \mathbf{R} \psi = \neg (\neg \varphi \mathbf{U} \neg \psi).$

It satisfies the following identity:

$\varphi \mathbf{R} \psi \equiv \psi \land (\varphi \lor \mathbf{X}(\varphi \mathbf{R} \psi)).$

This algorithm requires LTL formula to be in negative normal form.

Conversion to negative normal form:

- 1. Change all sub formulae like  $\mathbf{F} \varphi$  to true  $\mathbf{U} \varphi$ .

- 2. Change all sub formulae like **G**  $\varphi$  to false **R**  $\varphi$ .

- Using Boolean identities remove all logical operators except ¬, ∨, ∧.

- 4. Sink all negations inside temporal operators using following identities:

- 1.  $\neg(\varphi \mathbf{U} \psi) \equiv \neg \varphi \mathbf{R} \neg \psi$ ,

2.

$$\neg(\varphi \mathbf{R} \psi) \equiv \neg \varphi \mathbf{U} \neg \psi$$

,

3.  $\neg \mathbf{X} \varphi \equiv \mathbf{X} \neg \varphi$ .

For algorithm we need following data structures:

- *UID* is unique identifier;

- *Formula* is LTL formula;

- *Node* is a vertex of transition graph of Buchi automaton.

The format of *UID* and *Formula* is not significant so describe a *Node* structure (listing 2.1).

#### Listing 2.1. Structure Node

```

struct Node

{

UID id;

list<NodeID> incoming;

list<Formula> old;

list<Formula> new;

list<Formula> next;

};

```

*Incoming* is a list of predecessor vertices (edges lead from this nodes to considered node). In the fields: *old*, *new* and *next* there are lists of sub formulae of source formula.

The function *CreateAutomaton* (listing 2.2) creates the transition graph of Buchi automaton from formula f.

#### Listing 2.2. Function CreateAutomaton

```

list<Node> CreateAutomaton (Formula f)

{

Node n;

n.incoming = {init};

n.old = Ø;

n.new = {f};

n.next = Ø;

return expand(n, Ø);

}

```

Function Expand is shown in listing 2.3.

#### Listing 2.3. Function Expand

```

list<Node> Expand (Node currentNode, list<Node> nodes)

{

if (currentNode.new == \emptyset)

{

if (3 Node r \in nodes: r.old == currentNode.old

&& r.next == currentNode.next)

{

r.incoming = r.incoming ∪ currentNode.incoming;

return nodes;

}

else

{

Node newNode;

newNode.incoming = {currentNode};

newNode.old = newNode.next = \emptyset;

newNode.new = currentNode.next;

Expand(newNode, nodes ∪ {currentNode});

}

}

else

// currentNode.new is not void.

{

Choose Formula n из currentNode.new;

currentNode.new = currentNode.new \ {n};

if (n \in currentNode.old) Expand(currentNode, nodes);

else

{

if (n == false or !n \in currentNode.old) return

nodes;

if (n \in AP \text{ or } ! n \in AP \text{ or } n == true)

// node replacement.

{

```

```

node newNode;

newNode.incoming = currentNode.incoming;

newNode.old = currentNode.old \cup {n};

newNode.new = currentNode.new;

newNode.next = currentNode.next;

Expand(newNode, nodes);

}

if (n has the form f \lor g)

// Replacement of node currentNode by node newNode.

node newNode1, newNode2;

newNode1.incoming = currentNode.incoming;

newNode1.old = currentNode.old \cup \{n\};

newNode1.new = currentNode.new \cup {f};

newNode1.next = currentNode.next;

newNode2.incoming = currentNode.incoming;

newNode2.old = currentNode.old \cup {n};

newNode2.new = currentNode.new \cup \{g\};

newNode2.next = currentNode.next;

Expand(newNode2, Expand(newNode1, nodes));

}

if (n has the form f U q)

// f U q \Leftrightarrow q \lor (f \land X (f U q)).

// Splitting.

{

node newNode1, newNode2;

newNode1.incoming = currentNode.incoming;

newNode1.old = currentNode.old \cup {n};

newNode1.new = currentNode.new \cup {f};

newNode1.next = currentNode.next \cup {f U g};

newNode2.incoming = currentNode.incoming;

newNode2.old = currentNode.old \cup {n};

newNode2.new = currentNode.new \cup \{q\};

newNode2.next = currentNode.next;

Expand(newNode2, expand(newNode1, nodes));

}

if (n has the form f \mathbf{R} g)

// f \mathbf{R} g \Leftrightarrow g \land (f \lor X (f \mathbf{R} g)).

// Splitting.

{

node newNode1, newNode2;

newNode1.incoming = currentNode.incoming;

newNode1.old = currentNode.old \cup {n};

newNode1.new = currentNode.new \cup {f};

newNode1.next = currentNode.next;

newNode2.incoming = currentNode.incoming;

```

```

newNode2.old = currentNode.old \cup {n};

newNode2.new = currentNode.new \cup {f, g};

newNode2.next = currentNode.next \cup {f R q};

Expand(newNode2, expand(newNode1, nodes));

}

if (n has the form f \land q)

// Replacement of node currentNode by node newNode.

node newNode;

newNode.incoming = currentNode.incoming;

newNode.old = currentNode.old \cup {n};

newNode.new = currentNode.new \cup {f, g};

newNode.next = currentNode.next;

Expand(newNode, nodes);

}

if (n has form X f)

// Replacement of node currentNode by node newNode.

node newNode;

newNode.incoming = currentNode.incoming;

newNode.old = currentNode.old \cup {n};

newNode.new = currentNode.new;

newNode.next = currentNode.next \cup {f};

Expand(newNode, nodes);

}

}

}

```

#### Model checking using Buchi automaton

}

Let there be given *Kripke* model and *LTL* formula whose execution on the model is needed to be checked. The general idea of the algorithm is as follows:

- From the denial of *LTL* formula equivalent *Buchi* automaton is constructed.

- Kripke model is also converted into a *Buchi* automaton.

- Third *Buchi* automaton is constructed as the intersection of the first two. This state machine will allow the paths of the original model which does not satisfy the *LTL* formula.

- If a language allowed by the constructed automaton-intersection is empty then verification is successful. Otherwise the path allowed by the automaton-intersection is a counterexample.

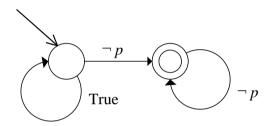

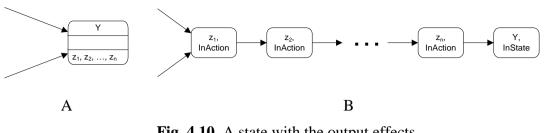

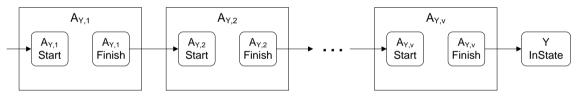

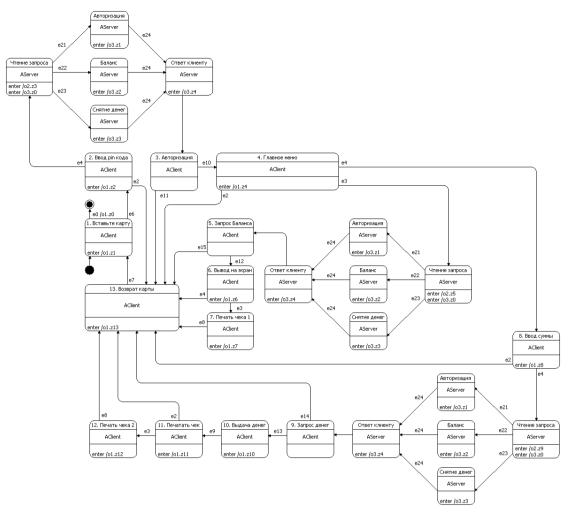

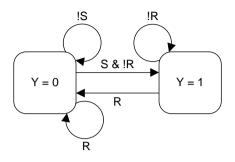

First we construct a *Buchi* automaton corresponding to the verifying *LTL*n formula. Recall what it represents. *Buchi* automaton is a finite automaton over infinite words. *Buchi* automaton transitions are marked by predicates of the original formula *LTL*. Automaton works as follows. At each step it takes a regular set of values of the predicate of the sequence, reflecting the history of the program. Using these values the automaton computes marks on the transitions from the current state. If there are more than one active transition, then automaton nondeterministically chooses one of them. The example of Buchi automaton constructed from LTL formula is shown in fig. 2.1. Formula "**GF** *p*" means that "*p* will be true indefinitely many times".

Fig. 2.1. The *Buchi* automaton for formula "GF p"

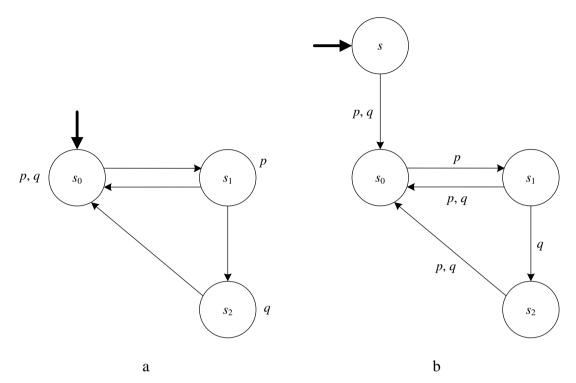

The next stage of verification is conversion *Kripke* model to *Buchi* automaton [17]. The example of *Kripke* model and corresponding *Buchi* automaton is shown in fig. 2.2.

After that the intersection of two these *Buchi* automata is constructed. Therefore it accepts only sequences of predicates that are accepted by the *Kripke* model and *Buchi* automaton. This intersection is a *Buchi* automaton. If the acceptance path is exists then:

- it is a possible scenario of the model;

- it violates verifying *LTL* formula.

Therefore it is a counter-example.

Рис. 2.15. Example of *Kripke* model (a) and corresponding *Buchi* automaton (б)

### 2.3. Model checking for branching temporal logic

A. Pnueli introduced the temporal logic into computer science for specification and verification of reactive systems [15]. Above *LTL* was considered - an important representative of the temporal logic. This logic is called linear, because when it is used a qualitative notion of time is linear: at any given time, there is only one child state, and therefore only one future. Formally speaking, this follows from the fact that the interpretation of temporal logic formulas, using the satisfiability relation  $\models$ , defined in terms of a model in which the state s has exactly one child R (s). Thus, for each state s model generates unique infinite sequence of states s, R (s), R (R (s)), ... The sequence of states is the calculation. As the semantics of linear temporal logic is based on such "generating sequence" models, the temporal operators **X**, **U**, **F** and **G** in fact describe the sequence of events along the one time way (one computing system).

In the early 80s for specification and verification was proposed another type of temporal logic, which is based not on the linear but on the branching notion of time. This logic is formally based on models, in which at each moment there may be several different possible futures. Given this notion of branching time temporal logic, this class is called branching temporal logic. Consequently, R (s) is a (nonempty) set of states, not one state, as in *LTL*.

Presentation of the semantics of branching temporal logic, therefore, is based on a tree of states instead of a sequence. Each path in this tree should present one possible computation. The tree itself represents all possible computations. More precisely, a tree, suspended in a state s, represents all possible infinite computations which start in state s.

Temporal operators in the branching temporal logic allow expressing properties (all or some) of the calculations in the system. For example, the property of **EF**  $\varphi$  means that there is a computation along which runs **F**  $\varphi$ . The essence of this property is that there is at least one possible computation, in which, ultimately status, performing  $\varphi$  is achieved. However, this does not exclude the fact that there may be computations, for which this property does not hold - calculations in which  $\varphi$  is never hold. The property **AF**  $\varphi$  for example, differs from this existential property of calculations the fact that it requires that all computations satisfy the property of **F**  $\varphi$ .

The existence of two types of temporal logic (linear and branching) led to the development of two "schools" of model checking. Despite the advantages and disadvantages of each of them, there are two reasons that justify consideration in this book both a model checking for linear and branching temporal logic:

- The expressive power of many linear and branching temporal logics is uncompared. This means that some of the properties expressible in linear temporal logic can not be expressed in some branching temporal logic and vice versa.

- Traditional methods used for efficient model checking for linear temporal logic are very different from the methods used for branching temporal logic. This leads, in particular, to quite different estimates of complexity.

This section focuses on model checking for branching temporal logic *CTL* (Computational Tree Logic). Importantly, it can be considered as an analogue of the branching *LTL*, for which it is possible an effective model checking.

Section outlines based on rate [1], and provides examples of [4, 26].

## 2.3.1. CTL syntax

Define syntax of *Computational tree logic* (*CTL*). Let  $p \in AP$ . By definition put Backus-Naur form

$\varphi ::= p \mid \neg \varphi \mid (\varphi \lor \varphi) \mid \mathbf{EX} \varphi \mid \mathbf{E}[\varphi \mathbf{U} \varphi] \mid \mathbf{A}[\varphi \mathbf{U} \varphi].$

The following atomic operators are used:

- EX (in the next state for some path);

- E (for certain path);

- A (for all paths);

- U (until).

**X** and **U** are linear temporal operators. They express properties on a fixed path. The quantifier **E** expresses a property on a certain path. The quantifier **A** expresses a property on all paths. The quantifiers **E** and **A** can be used only in combination with **X** or **U**. The operator **AX** is not atomic and is defined below. Boolean operators true, false,  $\land$ ,  $\rightarrow$  and  $\leftrightarrow$  have standard definitions.

From **F**  $\varphi$  = true **U**  $\varphi$  follows:

**EF**  $\varphi$  = **E**[true **U**  $\varphi$ ]; **AF**  $\varphi$  = **A**[true **U**  $\varphi$ ].

**EF**  $\varphi$  means " $\varphi$  comes true potentially". **AF**  $\varphi$  means " $\varphi$  is inevitable".

#### 2.3.2. CTL semantics

As marked above, the interpretation of LTL is defined in terms of sequence of states. *CTL* refers to many computational paths. So to adequately represent branching the concept of sequence was changed to concept of *tree*. *CTL* model is a model that generates tree. Like model *CTL model* is a triple M = (S, R, Label). The only difference is that *R* is a *total relation* instead of total function.

**Example**. Let  $AP = \{x = 0, x = 1, x \neq 0\}$  is a set of atomic propositions,  $S = \{s_0, ..., s_3\}$  is a set of states with following marks:

$Label(s_0) = \{x \neq 0\},\$  $Label(s_1) = Label(s_2) = \{x = 0\},\$  $Label(s_3) = \{x = 1, x \neq 0\},\$

transition relation *R* is following:

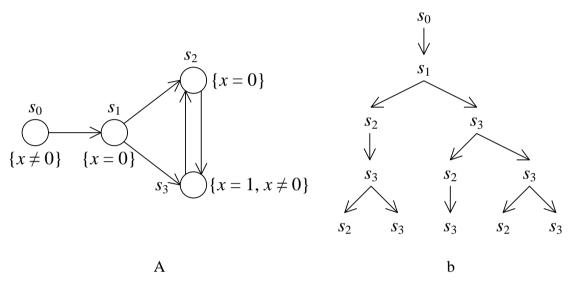

$R = \{(s_0, s_1), (s_1, s_2), (s_1, s_3), (s_3, s_3), (s_2, s_3), (s_3, s_2)\}.$ Consider CTL model M = (S, R, Label). It is shown in fig. 2.16 (a).

**Рис. 2.17.** Example of *CTL*-model (a) and a prefix of one of it's computational trees (b)

**Example.** Consider *CTL* model at fig. 2.16 (a). Finite prefix of infinite tree is shown in fig. 2.16 (b). Examples of paths are:  $s_0 s_1 s_2 s_3^{\omega}$ ,  $s_0 s_1 (s_2 s_3)^{\omega}$  and  $s_0 s_1 (s_3 s_2)^* s_3^{\omega}$ .

Semantics of *CTL* is also defined in terms of formula satisfiability relation  $(\models)$ .

Let  $p \in AP$  is atomic proposition, M = (S, R, Label) is *CTL* model,  $s \in S$  and  $\varphi, \psi - CTL$  formulae. By definition, put:

$$s \models p \qquad \Leftrightarrow p \in Label(s);$$

$$s \models \neg \varphi \qquad \Leftrightarrow \neg (s \models \varphi);$$

$$s \models (\varphi \lor \psi) \qquad \Leftrightarrow (s \models \varphi) \lor (s \models \psi);$$

$$s \models \mathbf{EX} \varphi \qquad \Leftrightarrow \exists \sigma \in P_M(s): \sigma[1] \models \varphi;$$

$$s \models \mathbf{E}[\varphi \mathbf{U} \psi] \qquad \Leftrightarrow \exists \sigma \in P_M(s): (\exists j \ge 0: \sigma[j] \models \psi \land$$

$$\wedge (\forall 0 \le k < j: \sigma[k] \models \varphi));$$

$$s \models \mathbf{A}[\varphi \mathbf{U} \psi] \iff \forall \sigma \in P_M(s): (\exists j \ge 0: \sigma[j] \models \psi \land \land (\forall 0 \le k < j: \sigma[k] \models \varphi)).$$

The Interpretation of temporal operators  $\mathbf{A}\mathbf{X}\varphi$ ,  $\mathbf{E}\mathbf{F}\varphi$ ,  $\mathbf{E}\mathbf{G}\varphi$ ,  $\mathbf{A}\mathbf{F}\varphi$  and  $\mathbf{A}\mathbf{G}\varphi$  can be produced from the definition.

# **Section 3. Verificators overview**

## 3.1. SPIN

*SPIN* [46] supports model checking and design of asynchronous process systems. There are four kinds of process interaction:

- *rendezvous* channels [46];

- buffered channels;

- shared variables;

- combined method.

*SPIN* supports an interactive and random simulation. In the interactive simulation non-deterministic choices are made by user. In the random simulation non-deterministic choices are made randomly.

SPIN accepts design specifications written in the verification language *PROMELA* (a *PROcess Meta Language*). The correctness claims must be specified in the synax of standard *Linear Temporal Logic (LTL)*.

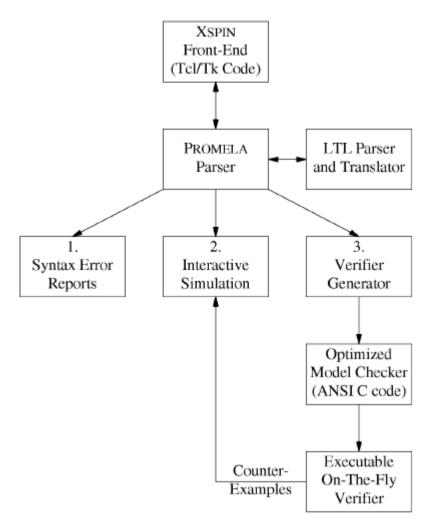

The basic structure of the *SPIN* model checker isillustrated in Fig. 3.1. The verification algorithms are based on convertation from *LTL* formula to the *Buchi automaton*.

Fig. 3.1. The structure of SPIN simulation and verification [46]

The syntax of *PROMELA* like the syntax of *C* language. The *PROMELA* model consists of the following components:

- type declaration (user-defined data-types);

- channel declaration;

- variable declaration;

- process declaration;

- the init process.

User-defined data types can be introduced by typedef declaration. Typedef declarations are like structures in C:

#### Listing 3.1. Typedef

```

typedef myType

{

int i;

byte arr[5]

};

```

User-defined data types can be used as elements of other user-defined data types:

Listing 3.2. Typedef

```

typedef myOtherType

{

myType t;

short s

};

```

PROMELA has five built-in variable types:

```

bit [0...1];

bool [0...1];

byte [0...255];

short [-2^{16}-1...2^{16}-1];

int [-2^{32}-1...2^{32}-1].

```

All variables should be declared. The default initial value of basic variables is 0. There are three ways which variable can be given a value:

assignment;

```

argument passing;

```

message passing;

Arrays are supported by *PROMELA*. Start index of arrays is 0.

The process can be considered as a procedure which runs in a separate thread. It has a local state which consists of *process counter* and local variables' values. The process declaration:

Listing 3.3. Declaration and definition of the process

```

proctype proc(int a; int b)

{

byte b; /* local variable */

/* process body */

}

```

The body of a process consists of a sequence of statements. A statement can be in one of two states: *executable* and *blocked*. The *executable* statement can be executed immediately. The *blocked* statement cannot be executed. An assignment is always executable. All expressions are the statements. Expression is executable if it evaluates to non-zero:

$4 \le 8$  is always executable.

a > 14 is executable if a greater than 14. Otherwise it's blocked.

x - 1 is executable if  $x \neq 1$ .

A *printf* statement is always executable. It is equivalent to *printf* function in *C*. It is not evaluated during verification.

The *skip* statement is always executable. It does nothing. The only result is increment of *process counter*.

The processes can have parameters and local variables. The active modificator means that the process is run in the initial system state. Processes are created using run statement:

Listing 3.4. Process running

```

init

{

run proc(1, 5);

}

```

The number of processes is bounded. This is because *PROMELA* defines finite state systems. The limit of active precesses in *SPIN* is 255. So *run* statement is only executable if it can create the process.